EDA辅助设计的那些事 点击:245 | 回复:6

楼主最近还看过

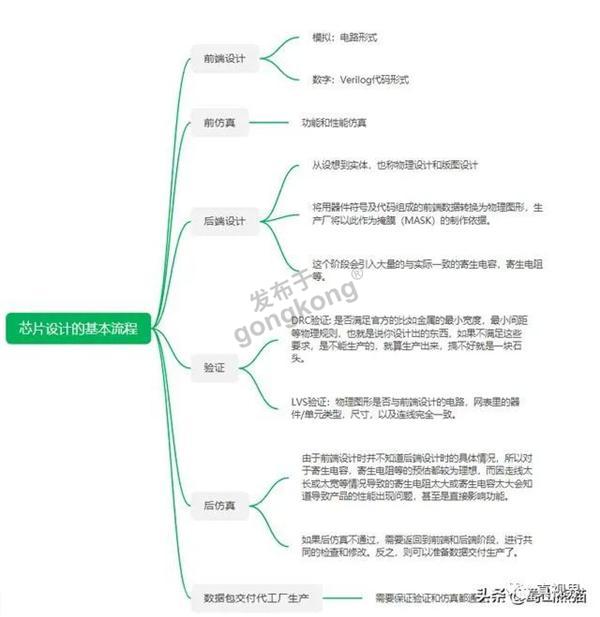

1)EDA的选择做了张脑图,大家先看下芯片的大致流程:

然后,我把设计流程里各个环节能用且好用的软件列一下(可以看到基本都是

PCB:

Allegro(Cadence) :这个还好,不更新也没太大个问题。

这里再简单说下国内的EDA情况,反向提图抄袭软件其实是走在世界前列的,芯X景(据说还要上市圈钱),客户除了早就被拉黑的外,都不敢说用了他家产品,怕吃官司,这种不值得提倡,因为他们干的事早已超出了他们所宣称的只用于合理学习的底线;

正向设计里目前真正得到认可的只有华大九天(我为他们点个赞),但主要是模拟产品上,具体的说是模拟电路的仿真工具(ALPS),再细化下是电源类产品的仿真上,有他们的独到及NB之处,他们也有对标 virtuoso的兼容性产品Aether,但是得在成熟工艺下用。国内的EDA依然处于一个辅助角色状态,还有很长很长的路要走。

Synopsys和Cadence一贯的发展战略是平台性发展,也就是说并不是某个环节的设计软件强,而是从前端设计-前仿真/验证-后端设计-后端验证仿真直到流片的整套产品都很强,并形成设计的闭环,比如synopsys的Milkway, Cadence的OA(OpenAccess)。

粗略的说,模拟/数模混合芯片设计用cadence平台,数字芯片设计采用synopsys平台,当然实际并非如此绝对,有一定的交叉使用情况。。对于客户来讲,他们自然会倾向于平台化的EDA的采购,而不是分门别类的买,因为省事就意味着省钱啊,除非你的某项产品极其NB,

比如Mentor的功能或物理验证产品,Ansys家的功耗分析软件,那确实厉害,尤其是物理验证C,S两家真干不过,已经是全球所有代工厂公认的金标准,也迫于垄断压力收不了,那只能战略合作。

3)与工艺厂的捆绑 (EDA联盟+IP联盟)

然后呢,EDA的垄断还体现在于工艺厂的捆绑上,工艺厂早期要进行工艺研发,势必也要进行器件,简单功能芯片的设计,要设计就得基于eda设计平台支持,这时候Synopsys, Cadence等EDA公司就来送温暖了,他们甚至会免费直接帮你设计多种基础IP, 各种规模的功能IP以扩充你的IP库,IP库越大越全,对客户的吸引力也就越大,win-win;

在功能验证,物理验证环节,则有Mentor的一席之地,物理验证会贯穿并频繁往返于后端设计的全流程,对于软件的效率和可视化要求很高,这点calibre做得非常好。另外EDA供应商还会给学校客户优惠价甚至免费,其目的也很明显,培养用户习惯,除非学校也是光荣的上了美帝黑名单。

也就是:EDA 工具+IP授权的捆绑。

这样一整,进入投产阶段后,工艺厂发给客户的PDK设计包自然也只能支持 Synopsys, Cadence,Mentor的了,其他的EDA替代品,多在兼容性上做功,并且无法提供平台化产品,加上兼容和原生,在时效及使用上都有很大的差异。

- JW-913 喷水织布机电气原理图...

[2664]

[2664] - 急寻锅炉液位监控系统!!!

[1490]

[1490] - 行车电器原理图

[1523]

[1523] - 63吨门式起重机需PG吗

[4427]

[4427] - 印 刷 常 识 浅 谈[转帖]

[2975]

[2975] - 谁有供水行业 PLC技术合同样...

[1528]

[1528] - 流浆箱操作

[4116]

[4116] - 不知道系统电抗计算为什么有...

[3404]

[3404] - 应用i.LON10(RNI)与WonderWa...

[1573]

[1573] - 电工证的种类

[2752]

[2752]

官方公众号

智造工程师

-

客服

客服

-

小程序

小程序

-

公众号

公众号

正在下载,请等待……

正在下载,请等待……

工控网智造工程师好文精选

工控网智造工程师好文精选