LabVIEWCompactRIO 开发指南34 在模拟模式下调试 点击:419 | 回复:0

LabVIEWCompactRIO 开发指南34

在模拟模式下调试

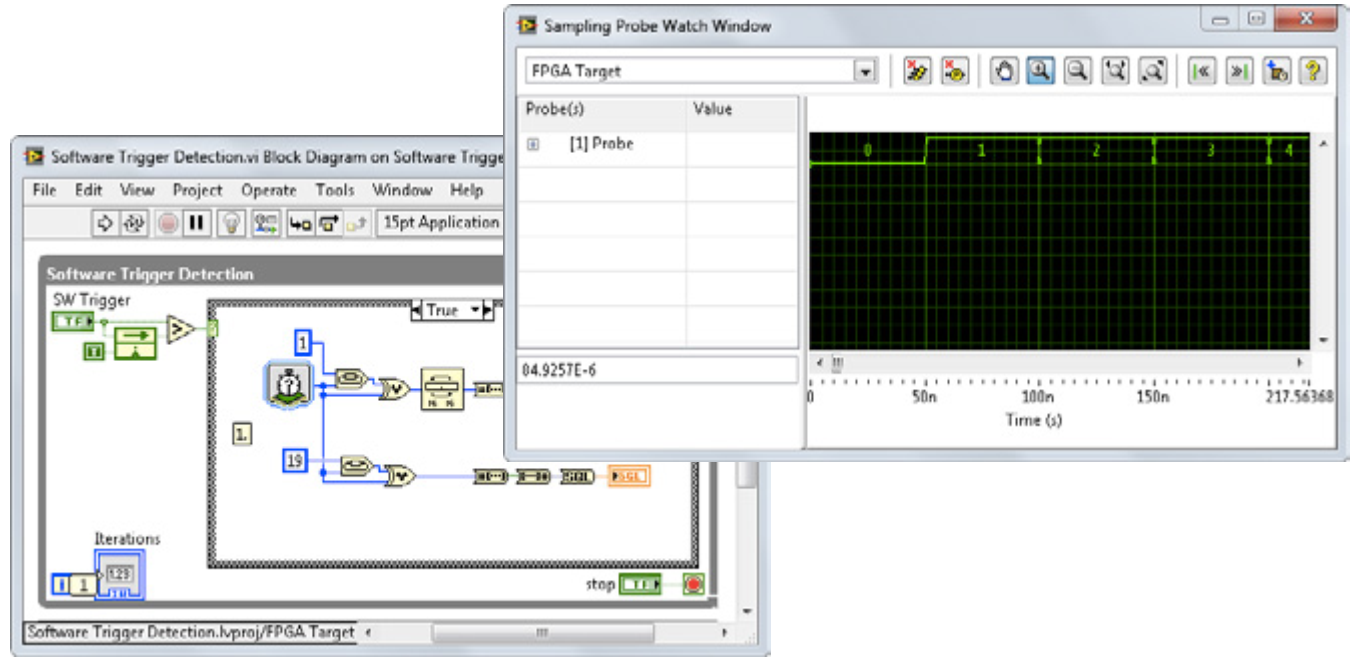

在仿真模式下执行LabVIEW FPGA VI时,可以访问标准LabVIEW调试功能,包括突出显示执行、探测和断点。LabVIEW2013及更高版本包含了一个额外的调试工具,称为采样探针。在仿真中运行时插入FPGA设计时,这些探头提供了一个独特的探针窗口,可以显示不同数字信号在时间方面的关系。

图5.30.查看信号之间相对于时间的关系

该窗口还包括用于定位信号上的下一个上升沿或上一个上升沿的功能,以及用于浏览数据的缩放功能。

在仿真中测试LabVIEW FPGA代码

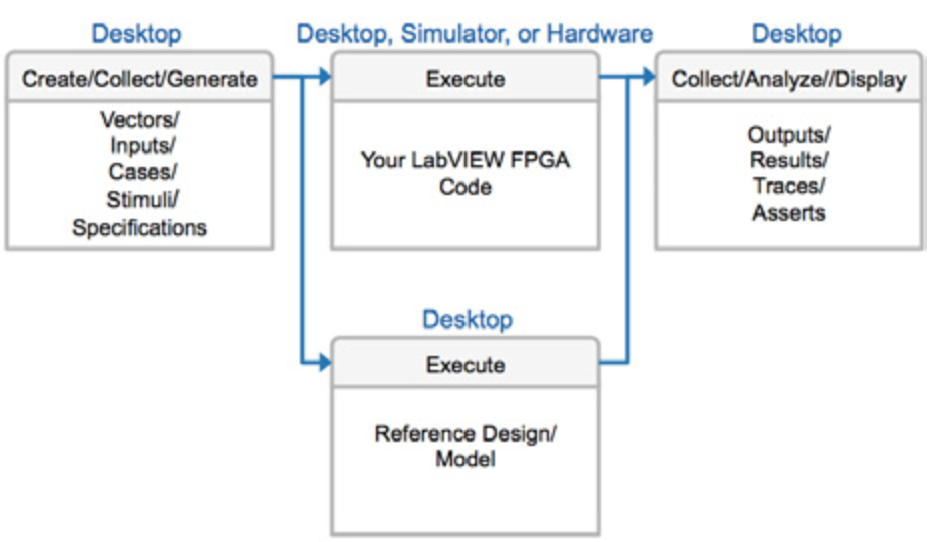

可以在LabVIEW中创建测试来练习LabVIEW FPGA。推荐的方法是让一个VI在主机(我的电脑或实时)环境中运行测试(或测试平台VI),LabVIEW FPGA VI在仿真模式或实际硬件中运行在FPGA环境中运行。由于测试平台VI在主机环境中运行,因此除了检查、分析、显示和报告测试结果外,还可以访问数百个函数来创建测试向量、案例和激励。

还可以使用相同的函数库来构建组件的参考实现。可以导入用C/C++或任何其他语言构建的实现,这些语言可以生成DLL或共享库,还可以利用对其他语言(的支持。图5.31提供了基本测试的示意图,所有测试都可以在LabVIEW图形化开发环境中实现。

图5.31.所有组件都可以在LabVIEW图形化开发环境中实现

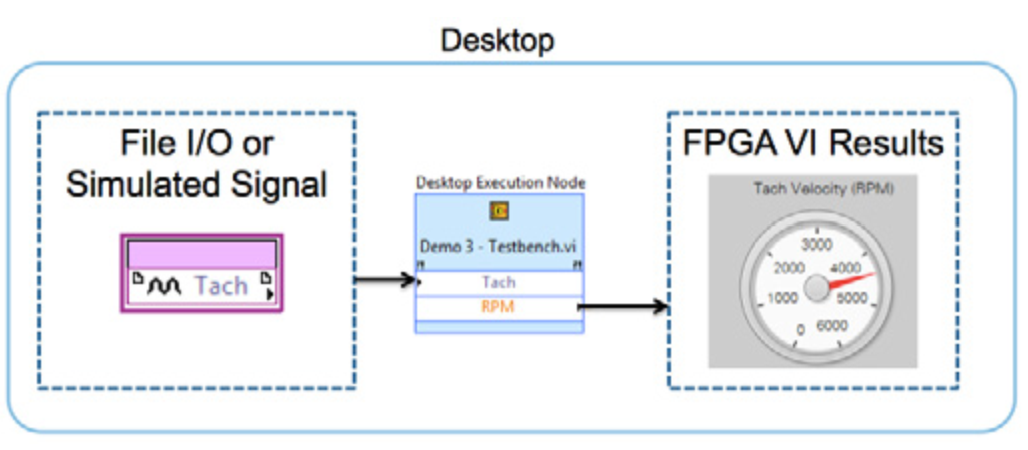

在LabVIEWFPGA模块版本2013及更高版本中,可以使用桌面执行节点测试LabVIEWFPGA组件。借助桌面执行节点,可以在LabVIEW FPGA VI上执行验证,而不必更改LabVIEW FPGA代码来适应测试需求。桌面执行节点使用模拟时间来反映硬件中的计时。可以在时间提前之前为控件、指示器和I/O提供激励;强制时间推进一定数量的ticks。然后在向VI提供额外激励之前读取控件、指示器和I/O的值。

图5.32.桌面执行节点可用于为LabVIEW FPGA VI创建测试台

了解模拟时间

要成功使用桌面执行节点,需要了解模拟时间的概念。从LabVIEW2013FPGA开始,开发人员在创建FPGA设计时可以考虑两种时序范式:wallclock time和仿真时间。wall clock time是一段逻辑执行可能需要的实际真实时间。使用位文件编程的FPGA设备以wall clock time运行。模拟时间是wallclock time的事件驱动模型。在执行期间,某些节点可能会宣布在特定时间需要时间步长。当LabVIEW检测到执行处于空闲状态时,模拟时间会前进到下一个最早的时间。

以下节点绑定到模拟时间并宣布时间步长或返回模拟时间值:

■While循环

■单周期定时循环

■Wait Express VI

■ LoopTimer Express VI

■ TickCount Express VI

■ FIFOsexcept DMA FIFOs

■ Waiton Occurrence and Wait on Occurrence with Timeout in Ticks

■ Interrupt VI when Wait Until Cleared isTRUE

需要说明的是,上述的例程和文档,都是可以下载的,双击即可打开,其中压缩文件是可以采用粘贴复制的方式,拷贝到硬盘上。这不是图片,各位小伙伴看到后尝试一下,这个问题就不用加微信咨询了。有关LabVIEW编程、LabVIEW开发等相关项目,可联系们。附件中的资料这里无法上传,可去公司网站搜索下载。

楼主最近还看过

- 如何打开后缀为EXB的文件

[2944]

[2944] - 谁有DeviceXPlorer OPC Serv...

[2054]

[2054] - 三菱PLC仿真软件GX Simulato...

[3396]

[3396] - OPC客户端(异步通知)+SQL的V...

[4559]

[4559] - 力控和PLC

[2722]

[2722] - WINCC通过OPC访问自身WINCC数...

[3438]

[3438] - 自整定pid算法

[5241]

[5241] - 安装好WINCC的电脑修改计算机...

[3768]

[3768] - 基于OPC的新一代组态软件 ic...

[2483]

[2483] - 工控网中令人厌恶的现象!

[2669]

[2669]

官方公众号

智造工程师

-

客服

客服

-

小程序

小程序

-

公众号

公众号

工控网智造工程师好文精选

工控网智造工程师好文精选