LabVIEWCompactRIO 开发指南28 可重入和非重入子VI之间的权衡 点击:391 | 回复:0

LabVIEWCompactRIO 开发指南28

了解可重入和非重入子VI之间的权衡

重入是子VI执行属性中的设置。在LabVIEW FPGA中,子VI执行默认设置为可重入。重入在FPGA逻辑中创建子VI的多个副本。这能够并行执行子VI的多个副本,同时存储不同且独立的数据存储。

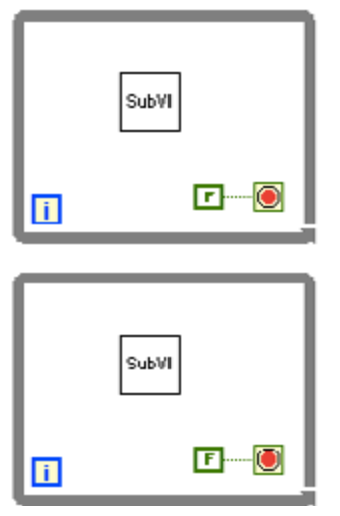

在图5.14的示例中,子VI设置为可重入,因此这两个循环同时运行,并且任何内部移位寄存器、局部变量或VI范围的存储器数据点对于每个实例都是唯一的。

图5.14.子VI设置为可重入

对于LabVIEWFPGA,这也意味着函数的每个副本都使用自己的FPGA,切入性对于代码可移植性是有效的,但可能使用更多门。如果尝试保存FPGA资源,则可能需要将执行属性更改为非重入执行。但是,对于小型子VI,在这种情况下,可能会使用更多的FPGA结构,因为编译器会向FPGA结构添加更多逻辑来处理仲裁。以下部分介绍避免仲裁的技术。

避免仲裁

当LabVIEWFPGA代码包含具有多个读取器或写入器的共享资源(例如I/O节点或不可重入子VI)时,就会发生仲裁。在这些情况下,编译器会向FPGA结构添加更多逻辑来处理此仲裁。如果担心尽量减少使用的FPGA结构的数量,请尽量避免仲裁。有关仲裁如何运作的更多信息,请参阅《LabVIEW FPGA Help Document: Managing Shared Resources》。

如上述帮助文档所述,可以通过更改LabVIEW中的仲裁设置来避免仲裁,但更可靠的技术是以防止仲裁的方式设计应用程序。下面列出了其中一些技术:

■最小化共享资源

■在时间关键型代码(如FIFO)中使用double-sided资源

■避免多个读取器和/或写入器到double-sided资源

另一种技术是在需要多个编写器的情况下创建多个全局或局部变量。例如,考虑使用LabVIEW FPGA VI,它使用一个环路从模拟输入节点读取数据,使用两个额外环路来处理模拟数据。在这种情况下,可以创建两个单独的全局或局部变量,例如A和B,以写入模拟输入环路。在第一个处理循环中,可以从变量A读取,在第二个处理循环中,可以从变量B读取。

创建计数器和计时器

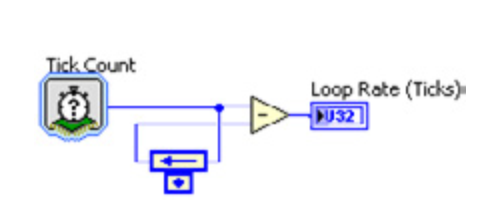

如果需要在一段时间后触发事件,请使用Tick Count函数测量经过的时间,如图5.15所示。不要使用内置于While循环和SCTL中的迭代终端,因为它最终会在其最大值时饱和。这发生在循环的2,147,483,647次迭代之后。在40MHz时钟速率下,这只需要53.687秒。相反,使用无符号整数和反馈节点以及Tick Count函数创建自己的计数器,以根据40MHzFPGA时钟提供时间。

图5.15.使用Tick Count测量经过的时间

由于对计数器值使用无符号整数,因此当计数器滚动更新时,已用时间计算将保持正确。这是因为如果使用无符号整数从一个计数值中减去另一个计数值,即使计数器溢出,仍然可以得到正确答案。

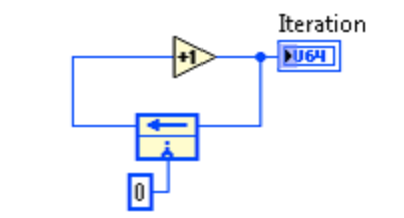

另一种常见的计数器类型是迭代计数器,用于测量循环执行的次数。无符号整数通常是迭代计数器的首选,因为它们在滚动更新之前提供最大的范围。用于计数器的无符号64位整数数据类型提供了巨大的计数范围,相当于大约180亿。即使FPGA时钟以40MHz运行,该计数器14,000年也不会溢出。

图5.16.无符号整数通常是迭代计数器的首选

需要说明的是,上述的例程和文档,都是可以下载的,双击即可打开,其中压缩文件是可以采用粘贴复制的方式,拷贝到硬盘上。这不是图片,各位小伙伴看到后尝试一下,这个问题就不用加微信咨询了。有关LabVIEW编程、LabVIEW开发等相关项目,可联系们。附件中的资料这里无法上传,可去公司网站搜索下载。

楼主最近还看过

- 工控网中令人厌恶的现象!

[2669]

[2669] - 困惑:没人提到却非常重要的问...

[2346]

[2346] - 监控组态软件的发展趋势与现...

[17102]

[17102] - 【经验分享】如何设计3d视觉效...

[2480]

[2480] - PLC试题参考

[25317]

[25317] - 完全免费的强大组态软件“态神...

[5838]

[5838] - S7-200 PLC仿真软件 免费软...

[4603]

[4603] - 请问labview价格!

[2473]

[2473] - 每天电脑重启后打开SIMATIC ...

[2102]

[2102] - 三谁能告诉我安装三菱中文版...

[2564]

[2564]

官方公众号

智造工程师

-

客服

客服

-

小程序

小程序

-

公众号

公众号

工控网智造工程师好文精选

工控网智造工程师好文精选