LabVIEWCompactRIO 开发指南25 实施LabVIEW FPGA代码的方法 点击:69 | 回复:0

LabVIEWCompactRIO 开发指南25

实施LabVIEW FPGA代码的方法

开始开发时,应在LabVIEW项目的FPGA目标下创建VI,以便使用LabVIEW FPGA选板进行编程,该选板是LabVIEW选板的子集,包括一些LabVIEW FPGA特定函数。

应该在仿真模式下开发VI,方法是右键单击FPGA目标并选择执行ExecuteVI

on»Development Computer with Simulated I/O。通过采用这种方法,可以快速迭代设计并访问所有标准LabVIEW调试功能。如果需要访问实际的I/O,请将执行模式更改为在Execute VI on»FPGA Target。

读取和写入I/O

本节介绍了通过LabVIEW FPGAVI访问I/O的基本知识。有关使用LabVIEW FPGA的模拟和数字I/O模块定时和同步的更多详细信息,请参阅第6章:I/O的定时和同步。

要开发LabVIEWFPGA应用程序,需要将FPGA目标添加到LabVIEW项目中,以及任何必要的I/O、时钟、寄存器项、内存项或FIFO。LabVIEW帮助文档在LabVIEW项目中使用FPGA目标提供了如何设置的详细说明。

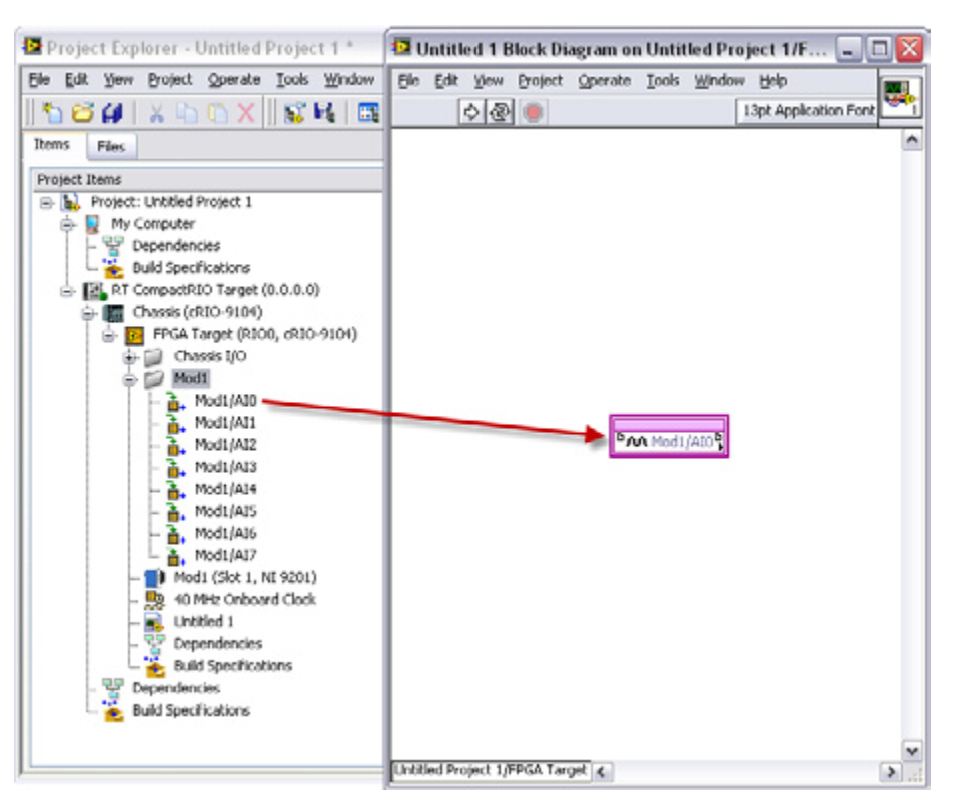

一旦将LabVIEW项目配置为面向FPGA设备,即可将I/O通道从LabVIEW项目拖放到LabVIEW FPGAVI框图上,以获取I/O节点。

图5.3.将I/O节点拖放到FPGA框图中。

FPGAI/O节点在调用时返回单点数据。对于大多数NIR系列设备和C系列I/O模块,可以使用LabVIEW结构和逻辑来指定采样率和触发。使用Δ-Σ转换器并具有自己板载时钟的高速模拟输入模块是一个例外。对于这些模块,可以使用属性节点控制采样率。第6章:I/O的定时和同步中的表6.2提供了使用三角积分调制的NIC系列I/O模块的列表。

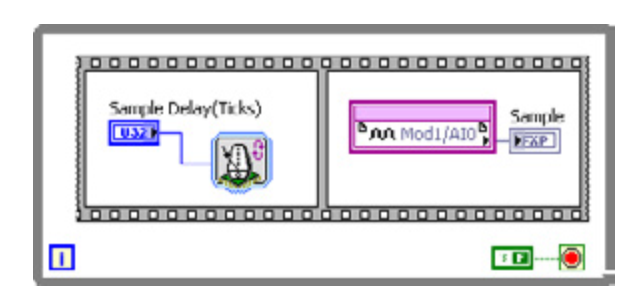

对于大多数I/O节点,可以使用带有快速循环定时器VI的环路来设置采样率。样本延迟控件以刻度为单位设置速率。Ticks是FPGA时钟上的脉冲,对于大多数CompactRIO目标,其默认为40MHz。例如,在40MHz时钟上实现20,000个时钟周期的采样延迟,则采样速率为2kHz。还可以通过双击循环计时器,调整配置面板来指定以微秒或毫秒为单位的延迟。当然,无论指定什么速率,模块采样最多只能达到模块文档中指定的最大速率。

可以选择使用Sequence结构,如图5.4所示。序列结构可用于保证每次编译LabVIEW FPGA VI时,定时器和I/O节点都以相同的顺序执行。

图5.4.标准模拟输入模块的采集方案

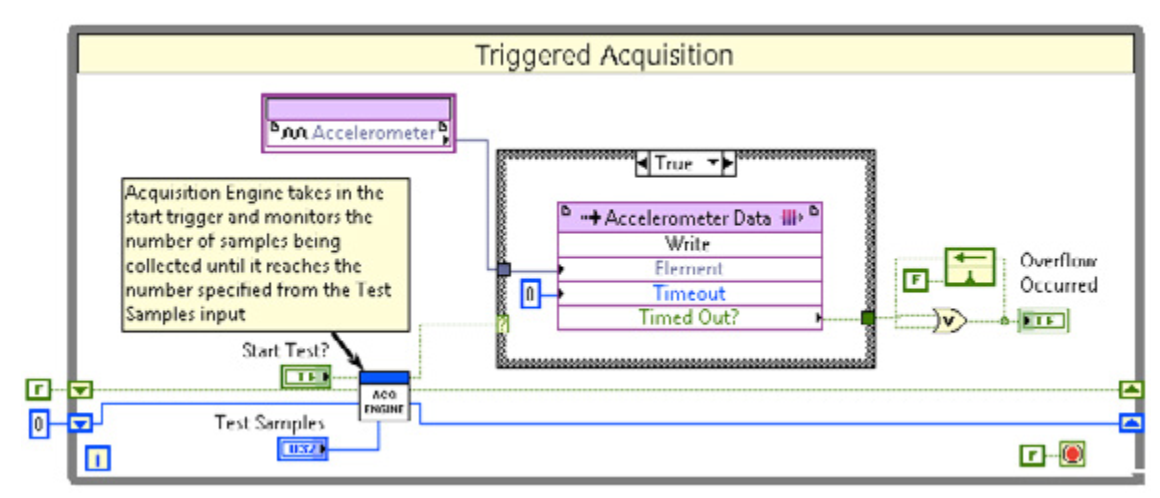

若要实现触发的应用程序,请使用对触发条件进行门控的案例结构。此触发条件可以是来自主机处理器的输入,也可以直接从FPGA上的逻辑派生。借助LabVIEW FPGA,可以实现基本或复杂的触发方案,例如重新触发、暂停触发或任何类型的自定义触发。图5.5显示了一个应用程序示例,该应用程序采用启动触发器并监视正在收集的样本数,直到达到用户指定的数量。此示例中使用的代码可以在涡轮机测试仪项目中找到,该项目可以从ni.com/compactriodevguide的Introductionand Basic Architectures部分下载。

图5.5.简单的单触发

需要说明的是,上述的例程和文档,都是可以下载的,双击即可打开,其中压缩文件是可以采用粘贴复制的方式,拷贝到硬盘上。这不是图片,各位小伙伴看到后尝试一下,这个问题就不用加微信咨询了。有关LabVIEW编程、LabVIEW开发等相关项目,可联系们。附件中的资料这里无法上传,可去公司网站搜索下载。

楼主最近还看过

- 组态王受干扰自动退出?

[2621]

[2621] - 请问哪里有OMRON PLC编程软...

[3427]

[3427] - 组态王的售后服务不错

[1997]

[1997] - 温度PID控制

[2194]

[2194] - intouch 2012 ,传说中intouc...

[5198]

[5198] - 组态王_实例

[11227]

[11227] - 中科新控监控组态软件SIAVIE...

[2177]

[2177] - 每天电脑重启后打开SIMATIC ...

[2102]

[2102] - 免费提供PLC培训视频教程

[2744]

[2744] - 组态王的自定义函数.

[2368]

[2368]

官方公众号

智造工程师

-

客服

客服

-

小程序

小程序

-

公众号

公众号

工控网智造工程师好文精选

工控网智造工程师好文精选