LabVIEW如何优化FPGA可用资源或提升速度 点击:275 | 回复:0

LabVIEW如何优化FPGA可用资源或提升速度

当编译FPGA代码时,由于过度映射 (overmap),未能满足时序要求或无法以所需的循环速率执行,导致编译失败。可以采取哪些步骤来优化FPGA代码并解决这些问题?

解决方案

减少门的使用并提高速度:

避免使用大型VI

编译后,会生成一个报告,提供有关已编译VI的速度和大小的信息。 设备使用摘要部分提供有关所用slices数量的信息。此评估标准是硬件上已编译程序大小的最重要指标。设计过程应该是一个迭代过程。在此过程中,随着程序变大,使用的slices可能会增加,从而可以确定何时空间不足。

使用单周期定时循环(SCTL)来优化代码

任何放入SCTL的LabVIEW FPGA代码都被针对性能进行了优化,并且消除了所有额外的逻辑强制数据流。因此,将部分代码放入SCTL并简单地将true连接到停止条件(仅运行一次)将创建优化的代码,从而减少FPGA使用并允许您为代码指定时钟源。

使用适当的仲裁

可重入子VI中的共享资源导致仲裁以防止竞争状况和同时访问。仲裁消耗大量FPGA资源,并且可能阻碍并行执行,因为代码的某些部分无法继续执行,直到资源再次释放。

只减少门资源的使用:

限制前面板数组

由于FPGA需要双缓冲,因此前面板上的数组占用了大量的空间。前面板数组控件和显示控件可以用DMA FIFO,实例化块存储器,索引表或程序框图常量来替代。

最少化前面板元素

FPGA Main VI前面板上的每个元件都会创建一个寄存器,以便主机可以与FPGA进行通信。此过程在FPGA上消耗额外的门资源。如果您不需要与主机端通信,请将这些控件转换为常量或全局变量。

用基于二进制逻辑的计算替换算术面板子VI

对于某些情况,函数面板子VI(例如商与余数 ,大于?,和判定范围并强制转换可以简化为二进制操作。这可能会大大降低FPGA上的门资源使用,但可能需要更多的时间来完成。

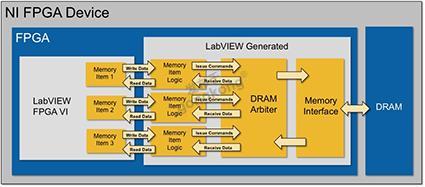

创建内存项和FIFO时使用内存块

在为FPGA目标创建存储器项和FIFO时,有几种选择可用于在硬件上创建实例。其中一些(例如触发器或查找表执行)使用FPGA资源,这些资源可能是FPGA VI的其他部分所需要的。将这些替换为使用内存块,将释放这些资源以供其他部分的代码使用。程序框图中的大型数组也可能耗尽这些资源,因此在需要存储大量值时,请考虑使用内存选项。

将代码引入到主机端

有的时候一些处理不需要在 FPGA 中执行。也许程序中的部分可以在主机端执行,然后利用 DMA 或者 I/O 节点通信的方式将结果发送回 FPGA。

将FPGA代码分成多个部分

有时候FPGA 代码含有多个部分,而这些部分不需要在同一时间在芯片上执行。例如,一个特殊的测试有四个测试情况。可以创建四个独立的 FPGA 程序,在需要的时候从主机端下载并运行,而无需将这四种情况都放到一个程序中。

使用非重入子VI

默认情况下,所有LabVIEW FPGA VI都是可重入的,这将为使用的子VI的每一处调用分配新的资源。通过将某些子VI切换到非重入,这些子VI的调用都将使用相同的硬件资源。

只提高速度:

使用并行操作

FPGA编程的一个主要优点是能够在处理多个数据集或迭代时轻松实现并行执行。通过在代码部分创建并行程序,可以减少执行处理所需的总时间。由于FPGA VI默认是可重入的,因此可以像并行运行多个子VI一样简洁。

使用流水线技术

通过将顺序进程划分为可并行运行的离散步骤,流水线技术允许代码的多个部分同时运行。通过用这种方式处理数据的不同部分,可以加快代码运行的总速度。使用移位寄存器或反馈节点允许逻辑并行执行并同时处理多次迭代。。

更详细的内容,参加如下附件的介绍。

LabVIEW、LabVIEW开发、LabVIEW编程、LabVIEW程序

上文中提到的例子和资料,均在word中的附件里,可点击下载。进一步了解,可联系我们。

http://www.bjcyck.com/nd.jsp?id=398#_np=2_358

楼主最近还看过

- 施耐德PLC编程软件

[8895]

[8895] - Protel DXP使用漫谈

[6925]

[6925] - OPC客户端(异步通知)+SQL的V...

[4559]

[4559] - 自动化软件擂台第六期 组态软...

[2549]

[2549] - 三菱PLC维修实例

[4948]

[4948] - 请问哪里有组态王图库下载

[2259]

[2259] - 关于WINCC自动退出激活系统

[2419]

[2419] - 求助施耐德公司的 MP7与CON...

[6165]

[6165] - android版组态软件

[4249]

[4249] - 你被机床厂家忽悠了吗?

[4894]

[4894]

官方公众号

智造工程师

-

客服

客服

-

小程序

小程序

-

公众号

公众号

工控网智造工程师好文精选

工控网智造工程师好文精选