IS61WV204816ALL高速异步SRAM 点击:245 | 回复:0

ISSI IS61WV204816ALL是高速,32M位静态RAM,组织为2048K字乘16位。它是使用ISSI的高性能CMOS技术制造的。这种高度可靠的过程与创新的电路设计技术相结合,可生产出高性能和低功耗的设备。

当CS#为高电平(取消选择)时,器件将进入待机模式,在该模式下,可以通过CMOS输入电平降低功耗。通过使用芯片使能和OutputEnable输入,可以轻松扩展存储器。激活的LOWWriteEnable(WE#)控制存储器的写入和读取。数据字节允许访问高字节(UB#)和低字节(LB#)。

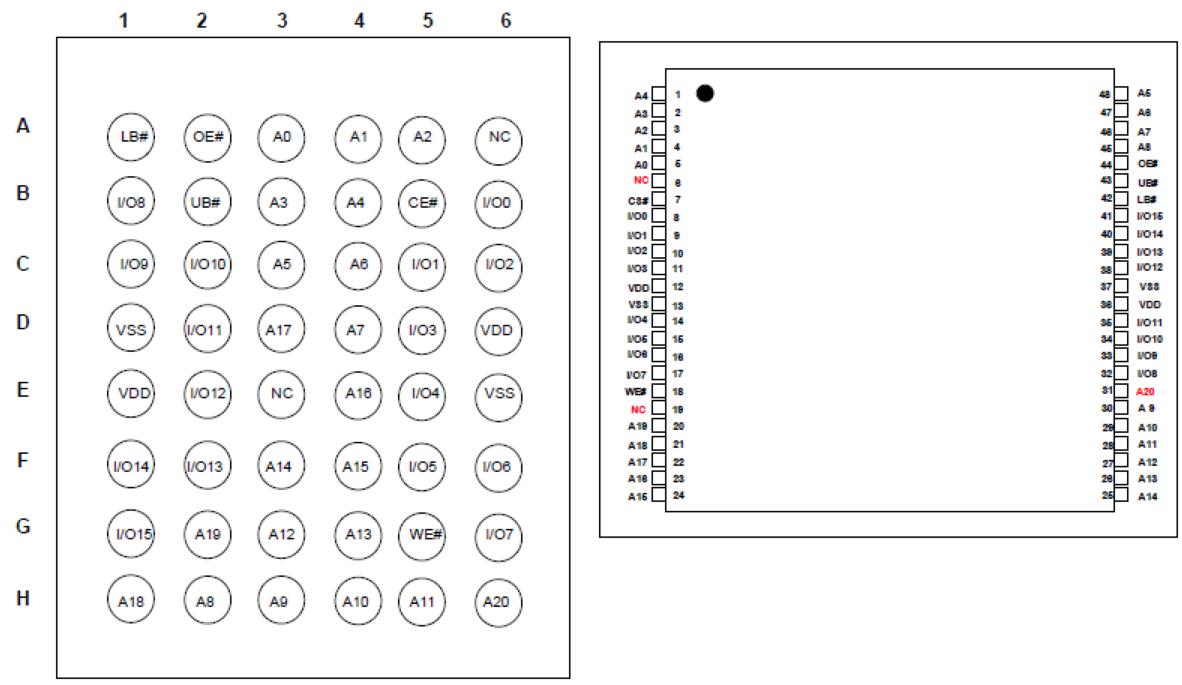

IS61WV204816ALL采用JEDEC标准的48引脚TSOP(TYPEI)和48引脚微型BGA(6mmx8mm)封装。

引脚配置

48针微型BGA(6mmx8mm) 48针TSOP,I型(12mmx20mm)

IS61WV204816AL特征

•高速访问时间:10ns,12ns

•高性能,低功耗CMOS工艺

•多个中心电源和接地引脚,可增强抗噪能力

•使用CS#和OE#轻松进行内存扩展

•TTL兼容的输入和输出

•单电源

–1.65V-2.2VVDD(IS61WV204816ALL)

–2.4V-3.6VVDD(IS61WV204816BLL)

•可用软件包:

-48球迷你BGA(6mmx8mm)

-48引脚TSOP(I型)

•工业和汽车温度支持

•可用无铅

•数据控制的高低字节

功能说明

sram是随机存取存储器之一。每个字节或字都有一个地址,可以随机访问。SRAM支持三种不同的模式。每个功能在下面的“真值表”中进行了描述。

待机模式

取消选择时(CS#高),设备进入待机模式。输入和输出引脚(I/O0-15)处于高阻抗状态。此模式下的CMOS输入将最大程度地节省功率。

写模式

所选芯片(CS#)和写入使能(WE#)输入为低电平时的写操作问题。输入和输出引脚(I/O0-15)处于数据输入模式。即使OE#为LOW,在此期间输出缓冲区也会关闭。UB#和LB#启用字节写入功能。通过使LB#为低电平,来自I/O引脚(I/O0至I/O7)的数据被写入地址引脚上指定的位置。且UB#为低电平时,来自I/O引脚(I/O8至I/O15)的数据被写入该位置。

读取模式

选择芯片时(CS#为低电平),写使能(WE#)输入为高电平时,读操作出现问题。当OE#为LOW时,输出缓冲器打开以进行数据输出。不允许在读取模式下对I/O引脚进行任何输入。UB#和LB#启用字节读取功能。通过启用LB#LOW,来自内存的数据将出现在I/O0-7上。且UB#为LOW时,来自内存的数据将出现在I/O8-15上。

在READ模式下,可以通过将OE#拉高来关闭输出缓冲器。在这种模式下,内部设备作为READ进行操作,但I/O处于高阻抗状态。由于器件处于读取模式,因此使用有功电流。

上电初始化

该器件包括用于启动上电初始化过程的片上电压传感器。

当VDD达到稳定水平时,器件需要150us的tPU(上电时间)来完成其自初始化过程。

初始化完成后,设备即可正常运行。

楼主最近还看过

- 谁需要CoDeSys编程说明书

[3404]

[3404] - 使用语音识别密码的智能电话...

[1870]

[1870] - 单片机中晶振的作用

[2419]

[2419] - 求助模拟量模块产品,大侠救火...

[1091]

[1091] - 一个向往嵌入式系统的白痴的...

[1320]

[1320] - 各位老师好,请问Windows CE和...

[1586]

[1586] - 为什么要做可测试性设计(DFT...

[1449]

[1449] - 请问接私活收费的问题,收多少...

[1565]

[1565] - windowsxp embeded正版的开发...

[1144]

[1144] - 热电阻测温电路框图和原理图

[1349]

[1349]

官方公众号

智造工程师

-

客服

客服

-

小程序

小程序

-

公众号

公众号

工控网智造工程师好文精选

工控网智造工程师好文精选