Bamtone班通:不同基材介电常数对PCB阻抗的影响有多大? 点击:64 | 回复:0

![]()

PCB阻抗与基材介电常数大致成反比,在叠层、线宽、介质厚度都不变的前提下,介电常数越高,阻抗越小;介电常数越低,阻抗越大。对常见 microstrip/stripline 结构,在相同线宽和介质厚度下,特性阻抗会明显升高,需要加宽线宽或减小介质厚度来拉回目标值。

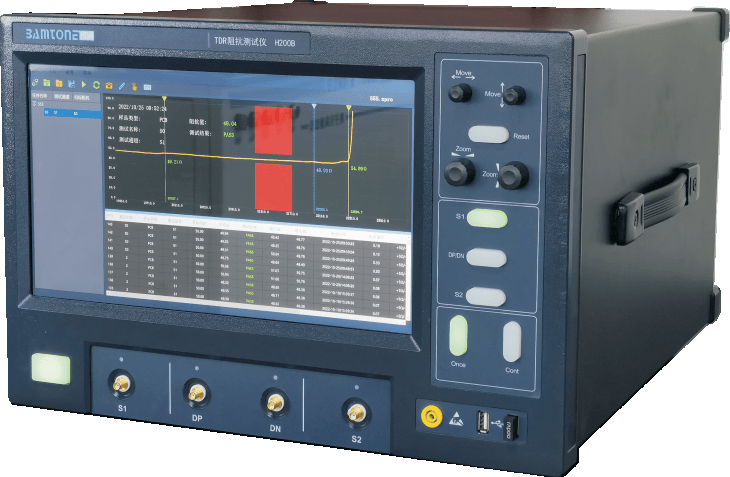

工程上,如果只把εr 从 4.3 调到 3.8 这一类“小变化”,阻抗通常会偏几欧姆到十欧姆量级,已经足以造成高速/高频链路不达标,所以阻抗计算时必须使用板厂给出的实测 Dk(分频段)数据,而不是“名义值”。作为国内领先的PCB测量仪器、智能检测设备等专业解决方案供应商,班通科技自研推出了PCB专用TDR阻抗测试仪Bamtone H系列,最高带宽高达20GHz,为广大PCB制造商在生产、设计过程中提供高效设备支持。

TDR阻抗测试仪Bamtone H200B系列

TDR阻抗测试仪Bamtone H200B系列

不同基材之间的差异?

通用 FR-4 在 1 GHz 左右的 εr 约 4.2–4.8,高速专用 FR-4 或混合树脂体系可以做到约 3.3–3.9,PTFE、低 Dk 复合材料可以进一步降到 2.x–3.x;在同样结构下,这些差异会带来几十个百分点的阻抗变化,需要配套不同线宽/介质厚度设计一整套阻抗库。陶瓷基板(如氧化铝、氮化铝)介电常数可达约 9–10,同样线宽和介质厚度下,阻抗会显著低于 FR-4,需要明显减小介电厚度或大幅减小线宽才能达到同样阻抗,因此高 Dk 材料常用于需要低阻抗、小型化或特殊热性能的场景。

对高速信号的工程影响有哪些?

介电常数越高,传播速度越慢、延迟越大,同时介质损耗往往也偏高,在长链路和高数据率下会加重码间串扰和眼图闭合,因此高速板材通常选择低且稳定的介电常数,并在阻抗、损耗、成本之间折中。由于 Dk 对频率、温度和含水率敏感,同一种材料在不同频点、不同环境下的“等效阻抗”也会轻微变化,所以做 10G、25G 及以上速率时,往往会限定材料的 Dk 公差和 Df(损耗角正切),并把这些参数带入仿真和阻抗计算,而不仅仅依赖名义 50 Ω 设计值。

楼主最近还看过

官方公众号

智造工程师

-

客服

客服

-

小程序

小程序

-

公众号

公众号

工控网智造工程师好文精选

工控网智造工程师好文精选