LabVIEWCompactRIO 开发指南33 测试和调试LabVIEW FPGA代码 点击:351 | 回复:0

LabVIEWCompactRIO 开发指南33

测试和调试LabVIEW FPGA代码

如前所述,应在仿真模式下开发LabVIEWFPGA VI,以快速迭代设计并避免冗长的编译时间。当需要测试和调试VI时,可以保持仿真模式或利用其他几个选项。应该根据功能验证与性能的要求以及要测试的代码类型(单元、组件或系统)选择执行模式。每种类型的代码都有不同的属性和验证要求,如下所述。

Unit

“Unit”是可以构建的最基本级别的IP,因为它映射到特定的处理函数或算法。不会拆分它并将其作为一组较小的功能单元进行测试。

希望保持这些简单,因此在以下情况下将其称为单位:

■它可以封装为用户可能希望在设计的其他部分重用的子VI

■不包括I/O、数据通信或任何目标资源

■它没有多个并行或以不同速率运行的回路

■它本质上是功能性的——可以提供一些已知的输入并测试预期的输出

■它可能保持状态,在这种情况下,可能需要多次调用它来验证它,但它的行为不应依赖于显式的特定时间流逝或控制

Component

Component是更复杂的逻辑片段,包括可能更关注系统中时序的元素。根据定义,它们是可组合的,并且通常具有明确的任务或目标要完成。FPGA应用通常可以分解为多个组件,此级别的验证可确保组件在集成到更大的组件中时按预期交互。可能还希望确保子组件与I/O或主机正确交互(通过主机接口),而无需等到整个系统组装完毕。

系统

可以将系统级别视为最顶层的组件。它由顶级FPGA VI以及通过组件级IP(CLIP)节点导入的任何其他HDLIP表示。它与其他组件有些不同,因为它的接口向主机应用程序公开,因此验证测试要么类似于运行主机应用,要么是主机应用。因此,验证需要使用主机接口API以及将实际I/O信号连接到系统。一个系统通常包含多个While循环或SCTL。

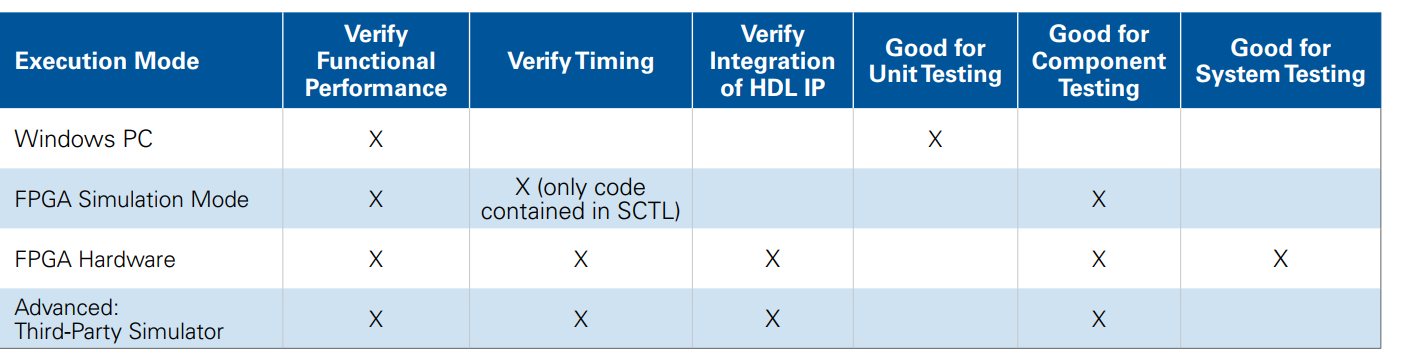

表5.2提供了有关应使用哪种执行模式进行验证和调试的指导。请记住,如果可以在单元和组件级别执行广泛的调试和验证,则可以减少系统级别的验证工作。

表5.2.用于验证和调试LabVIEW FPGA代码的不同执行模式

在WindowsPC上执行LabVIEW FPGA代码

可以通过将FPGA VI拖动到LabVIEW项目中的“我的电脑”目标,在WindowsPC上执行FPGA VI。这是调试、测试单元级代码的最快、最简单的方法。LabVIEW FPGA选板中包含的所有函数(不包括目标资源)都可以在桌面环境中执行。

这种方法有几个好处。为了进行调试,可以访问标准LabVIEWdebuging功能和可视化选项(图形、图表等)。出于测试目的,可以访问LabVIEW中的数个用于桌面编程选板的库。

在此上下文中,不要更改LabVIEW FPGA代码,因为不再被限制在有限的LabVIEW FPGA选板中,并且可能会引入仅在桌面上支持的结构。MyComputer执行环境是开发测试的理想选择,这些测试涉及围绕LabVIEW FPGA VI编写代码。

在模拟模式下执行

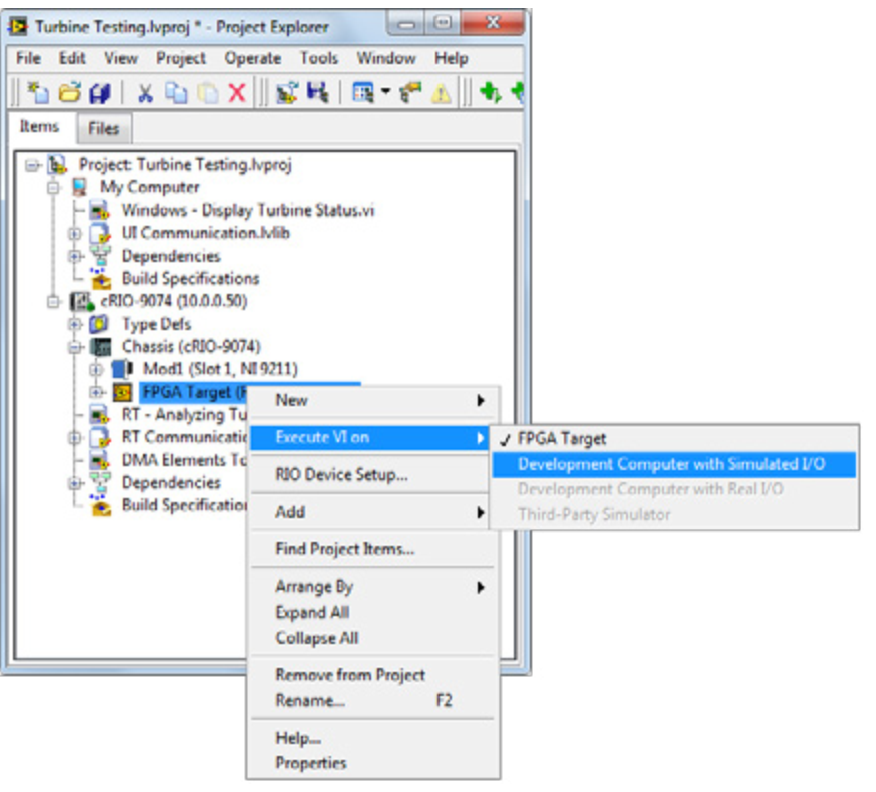

另一种选择是使用LabVIEW FPGA仿真。仿真使用内置的高保真、位精确仿真器在主机上执行FPGA代码。假设设计可以以所需的速率编译,则在仿真SCTL中包含的代码时,模拟器是周期精确的。该仿真器支持FPGA目标资源,如I/O、内存项和DMA FIFO,因此可以用于单元和组件级的代码。可以将LabVIEW FPGA VI配置为在仿真模式下运行,只需在LabVIEW项目中右击FPGA目标,然后选择在»Development Computer with Simulated I/O。

图5.29.更改LabVIEW FPGA VI的执行模式

需要说明的是,上述的例程和文档,都是可以下载的,双击即可打开,其中压缩文件是可以采用粘贴复制的方式,拷贝到硬盘上。这不是图片,各位小伙伴看到后尝试一下,这个问题就不用加微信咨询了。有关LabVIEW编程、LabVIEW开发等相关项目,可联系们。附件中的资料这里无法上传,可去公司网站搜索下载。

楼主最近还看过

- wincc6.0归档变量,存储位置选...

[2268]

[2268] - 应该学VB6.0还是学VB.NET

[4990]

[4990] - 分享一个软件-SMC气路图绘制

[13077]

[13077] - 实时数据库与组态软件、DCS系...

[2730]

[2730] - sql 2005+wincc62 sp2 asia下...

[3381]

[3381] - 告诉你西门子pcs7是什么东东

[7463]

[7463] - C#写的MobusTCP设备调试工具...

[1984]

[1984] - xArrow组态软件

[3123]

[3123] - intouch 2012 ,传说中intouc...

[5198]

[5198] - 组态王的售后服务不错

[1997]

[1997]

官方公众号

智造工程师

-

客服

客服

-

小程序

小程序

-

公众号

公众号

工控网智造工程师好文精选

工控网智造工程师好文精选