LabVIEW更高的吞吐量与更少的延迟2 点击:493 | 回复:0

LabVIEW更高的吞吐量与更少的延迟2

上一篇《LabVIEW更高的吞吐量与更少的延迟1》介绍了吞吐量的内容,本次介绍延迟的相关内容。

改善延迟

有一些技术可以解决改善延迟的问题。围绕这一目标的两个主要工具是实时操作系统和FPGA。

实时操作系统

任何操作系统都会遇到抖动或延迟变化。普通操作系统(如Windows)旨在尽可能公平地运行所有程序。为了促进这种公平性和时间共享,当操作系统循环运行其他进程时,给定程序中经常会出现抖动。抖动可以采取持续几毫秒的停顿形式,甚至长达数十秒。如果在某些情况下,抖动实际上是无限的。这种抖动限制了通用操作系统在以高度规律性执行任务时的有用性。这是因为它们是为公平性而不是可重复性而设计的,并且给定的任务在执行时间上会有很大的变化。

实时操作系统(RTOS)不是为了公平性而设计的,而是为了通过限制抖动来实现可重复性。这些例子包括Pharlap,VXWorks和R TLinux。操作系统的体系结构的目标是使给定的操作在固定时间内执行。这样,执行任务所需的时间是非常可预测和有规律的,抖动非常小。

通过额外的努力来减少抖动,RTOS上的一些操作平均比通用操作系统上的执行时间更长。但是,执行时间的实际上限可能要低得多。

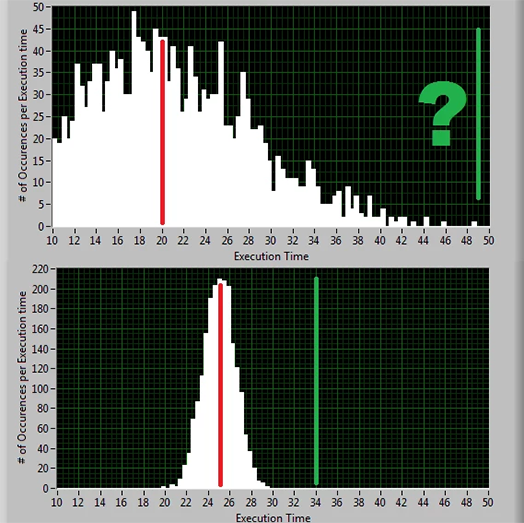

图:在两个操作系统上运行的控制环路的模拟环路时间。

顶部:通用操作系统的循环时间变化很大,没有实际的上限(绿线)。

底部:实时操作系统的平均值较高(红线),但抖动较少。这使其能够以更高的速率可靠地使用。

通用操作系统由于其高抖动,不适合应用于许多具有时序要求的应用。但是使用实时操作系统,PC可以部署到原本无法部署的情况下,因为它的执行时间更规律。尽管平均执行时间较长,但统计分布更窄,因此更可预测。最终效果是PC架构在无法以其他方式部署的应用程序中的能力得到增强。

虽然RTOS通过限制延迟的变化来提高PC的实用性,但它并没有降低其平均延迟。在需要大幅降低延迟的情况下,RTOS是不够的。

FPGA和延迟

已经开发了另一组工具来减少延迟。FPGA或现场可编程门阵列由基本节点的硬件“结构”组成。这些节点可以通过软件链接在一起以定义其行为,并轻松重新配置。FPGA具有硬件提供的极其精确的时序和可靠性以及软件开发的便利性。

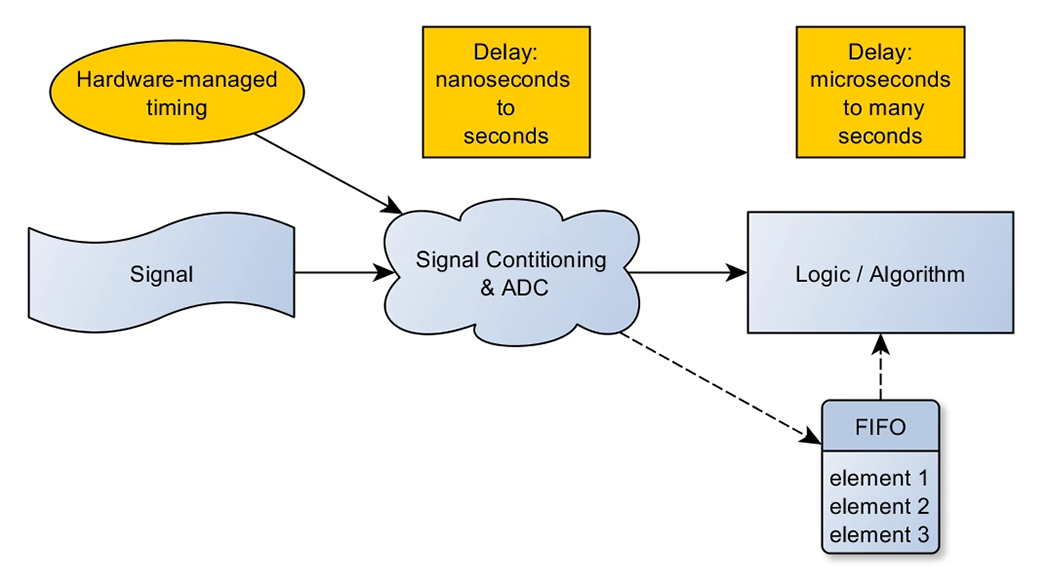

将算法放在FPGA上可以缩短从信号到算法的行程。在FPGA上,两个主要的延迟是ADC采样和算法的计算。此外,该算法的速度要快得多,因为它位于FPGA的硬件结构中,而不是软件执行系统中。它具有软件的灵活性,因为不需要对设备进行物理更改来更改其行为,但具有硬件的速度,以高达(目前)兆赫兹范围的时钟速率执行。

图 PGA架构和较短的算法行程(显示缓冲区的可选用法)

FPGA应用中的缓冲器是可选的-通常只包含在需要它们的计算中,例如FFT。不带缓冲器的FPGA代码是延迟最低应用最常选择的架构,在这些应用中,在给出输入后需要尽快获得结果。像这样的应用往往会尽快提供输出结果,就像在高速控制系统中一样。

FPGA和吞吐量

虽然在上一节中没有提到,但FPGA也是实现高吞吐量处理的有用工具。高吞吐量处理在FPGA上是可能的,因为算法是在硬件中执行的。通常,滤波、FFT或信号等预处理步骤在FPGA上运行,然后数据被缓冲并传递到主机PC。

如果同时想要高吞吐量和低延迟,该怎么办?

值得注意的是,大多数提高吞吐量的更改通常会对延迟产生负面影响。增加延迟的因素也会对吞吐量产生负面影响。可以同时满足两者的高度,但通常只能使用专用硬件或FPGA。幸运的是,大多数应用程序都需要其中之一,而不是两者兼而有之。

示例用例

想记录来自测试单元的振动测量值。有十几个应变通道,希望以至少50kHz的速度采样。对于NI硬件,可以使用DAQ设备来实现这,例如C系列NI-9237或PXI-4497。

对于此应用,采样速率很高,比软件定时要快得多。这是需要高吞吐量的系统示例。只要所有数据都到达日志文件,当发生这种情况时,它就不重要。因此,延迟不是主要问题。根据这些要求选择硬件时,吞吐量将是主要要求。FPGA并不重要,但需要高吞吐量、通道数、采样速度和磁盘空间。对于NI硬件,可以使用DAQ卡来实现这,例如C系列9237或PXI4497。

想为无人机运行基于模型的控制,这些循环时间中最快的需要在亚毫秒级别执行。该回路仅取决于一个传感器,但它对于在该时间执行的飞行器的稳定性至关重要。

涉及的通道并不多,尽管采样率需要高于软件定时速率,但吞吐量并不是主要问题。主要关注点是及时提供输出以满足固有的时序要求。因此,这是一个需要非常低延迟的应用程序示例。因此,将需要低延迟硬件,例如FPGA。如果要处理此应用程序,可能会从单板RIO开始。

想模拟射频通道。有一个4x4MIMO信号,并希望有一个系统模拟传输通道。希望测试实时运行。

该系统必须采集数据,对其进行处理,并在非常严格的时间间隔内返回结果。它还必须在多个通道上处理非常高的采样率。这是高吞吐量和低延迟应用程序的示例。对硬件的要求将是严格的,几乎肯定会需要专用硬件或强大的FPGA。借助NI硬件,可以使用NI矢量信号收发器(VST)完成这是最新的具有1GHz瞬时带宽,或者使用NI矢量信号分析仪(VSA)和随附的FlexRIOFPGA协置处理器。

想为飞机模拟飞行动力学模型,以便可以用它来测试飞行控制器。有数百个传感器和执行器,模型需要以至少1KHz的速率执行才能获得保真度。

该仿真系统对交付结果有严格的时序要求。由于如此高的通道数,它还具有高吞吐量。因此,此应用程序需要高吞吐量和低延迟。借助NI硬件,可以使用高速PXIExpress控制器(如PXIe-8135)和合适的I/O模块(部分包括FPGA)。

想获取一组压力和温度来监测设施的环境。速率不会超过每秒一个样本,预计每个样本之间的差异很小。使用这些值,将进行一些日志记录,并在值超出范围时发出警报。

此应用程序没有高吞吐量,因为数据速率很慢。它也没有严格的时序需求,因此不需要低延迟。软件时序足以满足此应用程序的需求。对硬件的要求并不严格,各种低成本的选择是可行的。

所以在设计一个系统时,“速度”有两个含义。“需要多快采集样本?”通常转化为吞吐量。“样本后需要多快获得结果?”通常转化为延迟。

需要说明的是,上述的例程和文档,都是可以下载的,双击即可打开,其中压缩文件是可以采用粘贴复制的方式,拷贝到硬盘上。这不是图片,各位小伙伴看到后尝试一下,这个问题就不用加微信咨询了。有关LabVIEW编程、LabVIEW开发等相关项目,可联系们。附件中的资料这里无法上传,可去公司网站搜索下载。

楼主最近还看过

- CVI4.0/5.0调用VC++6.0编译生...

[2453]

[2453] - 免费索取TRACE MODE6无限点免...

[3686]

[3686] - 免费下载:::绘图软件PCSchem...

[5598]

[5598] - 如何打开后缀为EXB的文件

[2944]

[2944] - 免费的3D组态软件态神v0.9携...

[10510]

[10510] - vb编写的串口调试程序(源代码...

[3668]

[3668] - Industry 4.0- 更为开放的需...

[2578]

[2578] - 求助:如何解决vb中不是已加载...

[3612]

[3612] - 工业自动化中常用的实时数据...

[5513]

[5513] - 求PLC 及其外围电路仿真软件

[3528]

[3528]

官方公众号

智造工程师

-

客服

客服

-

小程序

小程序

-

公众号

公众号

工控网智造工程师好文精选

工控网智造工程师好文精选