LabVIEW FPGA中可重入和非可重入子VI的区别 点击:452 | 回复:0

LabVIEW FPGA中可重入和非可重入子VI的区别

LabVIEW FPGAVI默认是可重入的。如果多次调用重入VI,则每个实例会占用FPGA器件的单独硬件资源。如果使用非重入VI,无论是并行多次调用还是仅调用一次,都只会创建一个硬件实例并将其用于该VI。

此默认行为与在非FPGA目标上运行的VI相反。在这种情况下,VI默认是不可重入的,并且一次只能在内存中打开一个实例。所有调用方都必须访问此同一实例。但是,当VI在非FPGA目标上可重入时,每次调用VI时,都会在内存中打开一个新实例。

使用非重入子VI的原因:

节省FPGA上的硬件空间和资源。

非重入VI在硬件中仅使用一个空间。如果FPGA应用中存在空间问题,可以将可重用的重复代码放入非可重入VI中,以节省空间并最大限度地减少资源使用。

非重入子VI可用于在独立环路之间存储和传输数据。

由于VI的所有调用方都使用同一组门,因此该VI的最后一次调用的值可供下一个调用方使用。

使用可重入子VI的原因:

主VI中只有一个子VI实例。

当只有一个实例时,两种执行模式之间都没有区别,也不需要更改默认行为。

在两个或多个独立循环中具有相同的子VI。

在并行循环中将子VI设置为非重入可能导致循环在同时调用子VI或在仍在执行时调用时相互等待。这可能会导致意外的抖动并减慢执行速度。

速度很重要,这不会达到FPGA的资源利用率限制。

程序相对较小,但需要在高频下保持确定性。

并行进程需要有自己的子VI实例,因此不会有数据从子VI的一个调用传输到下一个。

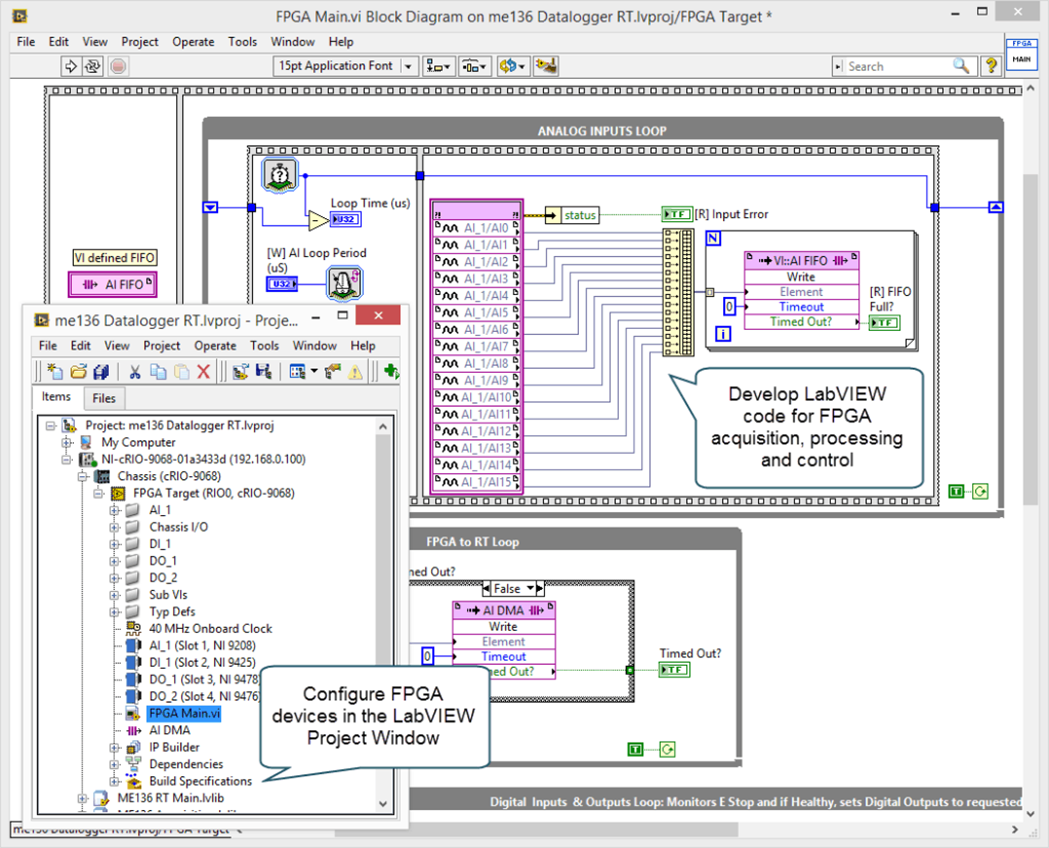

通过LabVIEW FPGA模块和LabVIEW创建运行在NI FPGA终端上的VI。可重配置I/O(RIO)设备可用作FPGA终端。FPGA终端包含一个由固定大小的I/O资源包围的可重配置FPGA(现场可编程门阵列)。根据具体的FPGA终端,固定的I/O资源可包括模拟和数字资源-例如,模数转换器(ADC)和数模转换器(DAC),通过FPGA可控制上述资源。

通过FPGA模块配置可重配置FPGA的动作以满足具体测量和控制系统的要求。运行于FPGA终端的VI称为FPGA VI。FPGA模块可用于创建FPGA VI。下载FPGA VI至FPGA的过程是对FPGA终端执行编程操作。用户创建和下载的每个新建FPGA VI均为一个自定义定时、触发和I/O解决方案。

需要说明的是,上述的例程和文档,都是可以下载的,双击即可打开,其中压缩文件是可以采用粘贴复制的方式,拷贝到硬盘上。这不是图片,各位小伙伴看到后尝试一下,这个问题就不用加微信咨询了。有关LabVIEW编程、LabVIEW开发等相关项目,可联系们。附件中的资料这里无法上传,可去公司网站搜索下载。

楼主最近还看过

- T-FACTORY 6 – 实时商业-生产...

[2211]

[2211] - DNP3.0、MB、MB+ 等通用数据采...

[2664]

[2664] - wincc6.0归档变量,存储位置选...

[2268]

[2268] - 请教工程师站和操作员站的区...

[8472]

[8472] - 请问组态软件中的一个点是什...

[2290]

[2290] - 所有的组态软件都是要钱的吗...

[2513]

[2513] - 求助:欲下载Protel99SE软件

[2931]

[2931] - 工控软件新品--TRACE MODE

[3049]

[3049] - 组态王怎样播放声音啊

[2831]

[2831] - WINCC通过OPC访问自身WINCC数...

[3438]

[3438]

官方公众号

智造工程师

-

客服

客服

-

小程序

小程序

-

公众号

公众号

工控网智造工程师好文精选

工控网智造工程师好文精选