LabVIEW通过IEC61508标准验证ITER联锁系统 点击:33 | 回复:0

LabVIEW通过IEC61508标准验证ITER联锁系统

保护环境要求系统能够保护机器免受工厂系统故障或机器危险操作造成的严重损坏。负责此功能的ITER系统是联锁控制系统(ICS)。该系统通过中央联锁系统(CIS)监督和控制不同的工厂联锁系统(PIS)和高级保护系统(APS),确保机器的完整性和可用性。

这些架构由冗余配置的NI-9159机箱组成。这些系统是使用高级图形编程工具LabVIEW FPGA开发的。IEC61508是适用于所有行业的功能安全标准。该标准定义了设计、部署和维护电气/电子/可编程电子(E/E/PE)安全相关系统的方法。它

ICS是负责保护托卡马克操作免受绝对工程限制的系统。投资保护危害在各个工厂中横向识别,ITER联锁完整性等级与IEC61508安全完整性级别相称。ITER使用与标准相同的按需故障概率目标。因此,

ICS执行具有不同时序要求的功能。一些要求要求控制器能够以亚毫秒级的响应时间提供互锁信号,需要严格的实时控制周期,其顺序为100μ秒.这些要求被分配给快速控制器。

快速控制器使用NI提供的基于Xilinx FPGA的COTSCompact RIO NI 9159。对故障、模式、影响和诊断分析进行了研究,以分析行为并提供架构解决方案。

Compact RIO技术为硬件开发和采集提供了节省成本的解决方案。控制器固件通过LabVIEWFPGA图形化编程工具开发。LabVIEW FPGA使开发人员能够创建设计,并直接将设计转换为配置流文件(位文件)。LabVIEW FPGA固件的编译步骤描述如下

中间文件的生成:LabVIEW的FPGAVI被转换为中间文件[超高速集成电路硬件描述语言(VHDL)代码],并准备发送给编译工作程序。

• 排队:挂起的作业由编译器服务器排队,稍后,它将中间文件发送到编译工作程序以进行编译过程。

• VHDL编译、分析和综合:数字逻辑元素由编译工作线程从中间文件创建。

• 映射:编译工作线程将逻辑分布在FPGA的物理构建块上。

• 放置和布线:逻辑被分配给FPGA的物理构建块,并建立逻辑块之间的连接以满足编译的空间或时序限制。

• 生成编程文件:编译工作程序创建二进制数据,并将其存储到LabVIEW创建的位文件中。

• 创建位文件:LabVIEW将位文件保存在项目目录的子目录中,并可以下载和/或在FPGAVI上运行应用程序。

LabVIEW生成VHDL代码,通过这些代码可以对FPGA进行编程,但用户无法直接访问这些代码。用户只能访问LabVIEW图形代码,且如上所述,该标准不为使用高级综合语言或图形语言开发的系统提供指令。此外,在无法访问自动生成的VHDL代码的情况下深入验证系统也很复杂。通过配置FPGA的最终代码进行验证过程。该进程应包括以下目标。

• 应验证单个单元功能的正确运行。

• 应验证组件之间的正确集成和通信。

• 应验证整个系统的行为。

要执行此任务,必须访问LabVIEW工具生成的中间VHDL代码,并对其应用测试技术。此外,建议使用经过认证的第三方VHDL编译器执行此过程。

第一个任务集中在有关代码分析和正确使用编译工具的IEC61508条款上。首先,对LabVIEW FPGA通过自动编译过程生成固件的步骤进行了详细研究。然后,尝试使用Xilinx工具复制LabVIEW编译自动生成的FPGA配置比特流。最后,可以创建一个TCL脚本,该脚本使用Xilinx ISE工具生成的结果结果与从LabVIEW编译获得的结果结果完全相同。

通过LabVIEW外部的仿真器运行固件的功能仿真是否可行,测试了实施此过程。MentorGraphics的第三方工具Questa高级模拟器用于运行模拟。测试平台是使用System Verilog语言开发的,并结合了先进的测试技术,例如:

• 代码覆盖率。

• 通过SystemVerilog断言实现功能覆盖。

• 刺激随机化。

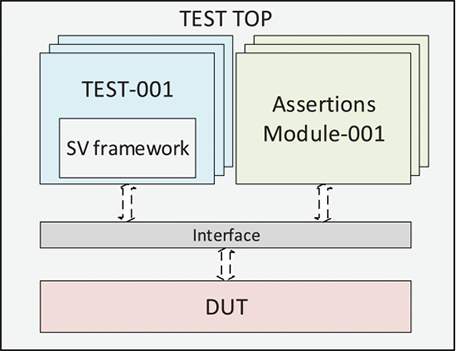

创建SystemVerilog仿真框架。它是一个典型接口和转移代理类库,用于加快新测试的开发和将V&V过程应用到新模板。一套n创建了测试,每个要测试的模块都有一个测试。此外,每个测试都包含一个断言模块,该模块实现功能覆盖并验证是否符合旨在验证每个测试的系统要求。为了标准化给定模块的断言和测试平台与被测设备之间的连接,必须使用System Verilog接口。

根据ITERICS-FA上的IEC61508标准,V&V工艺的应用一系列可能性和局限性。它确保接受所使用的COTS设备适合在投资保护环境中运行的必要保证。

基于所获得的结果,提出了适用于ICS-FA的优化V&V方法。因此,可以得出结论,系统的V&V是可能的,但有一些限制。一方面,不可能涵盖标准的所有项目,使标准部分适用。另一方面,必须考虑到应用此过程所需的巨大努力和时间成本。特别是,首次理解、管理和实施此过程所需的工作量非常高。即便如此,随后的执行次数也需要付出很大的努力。当前基线中的几个关键系统,如中断缓解系统或超导磁体保护,可能会经历所描述的极其谨慎的V&V过程。然而,如果以有限和有针对性的方式应用,所确定的技术也可以使低临界系统受益。

此外,还考虑了开发安全系统的两个必要方面。首先,研究证明了在基于NI9159的应用中集成SEU检测和缓解系统的必要性和可能性。其次,它发现了如何控制FPGA的放置并隔离LabVIEW中引入的VHDL模块,从而揭示了单芯片容错在CIS-FA设计中的相关位置。

这是LabVIEW的一个应用,更多的开发案例,欢迎登录北京瀚文网星官网,了解更多信息。有需要LabVIEW项目合作开发,请与我们联系。

楼主最近还看过

官方公众号

智造工程师

-

客服

客服

-

小程序

小程序

-

公众号

公众号

工控网智造工程师好文精选

工控网智造工程师好文精选