LabVIEWCompactRIO 开发指南32 确保无损数据传输 点击:313 | 回复:0

LabVIEWCompactRIO 开发指南32

确保无损数据传输

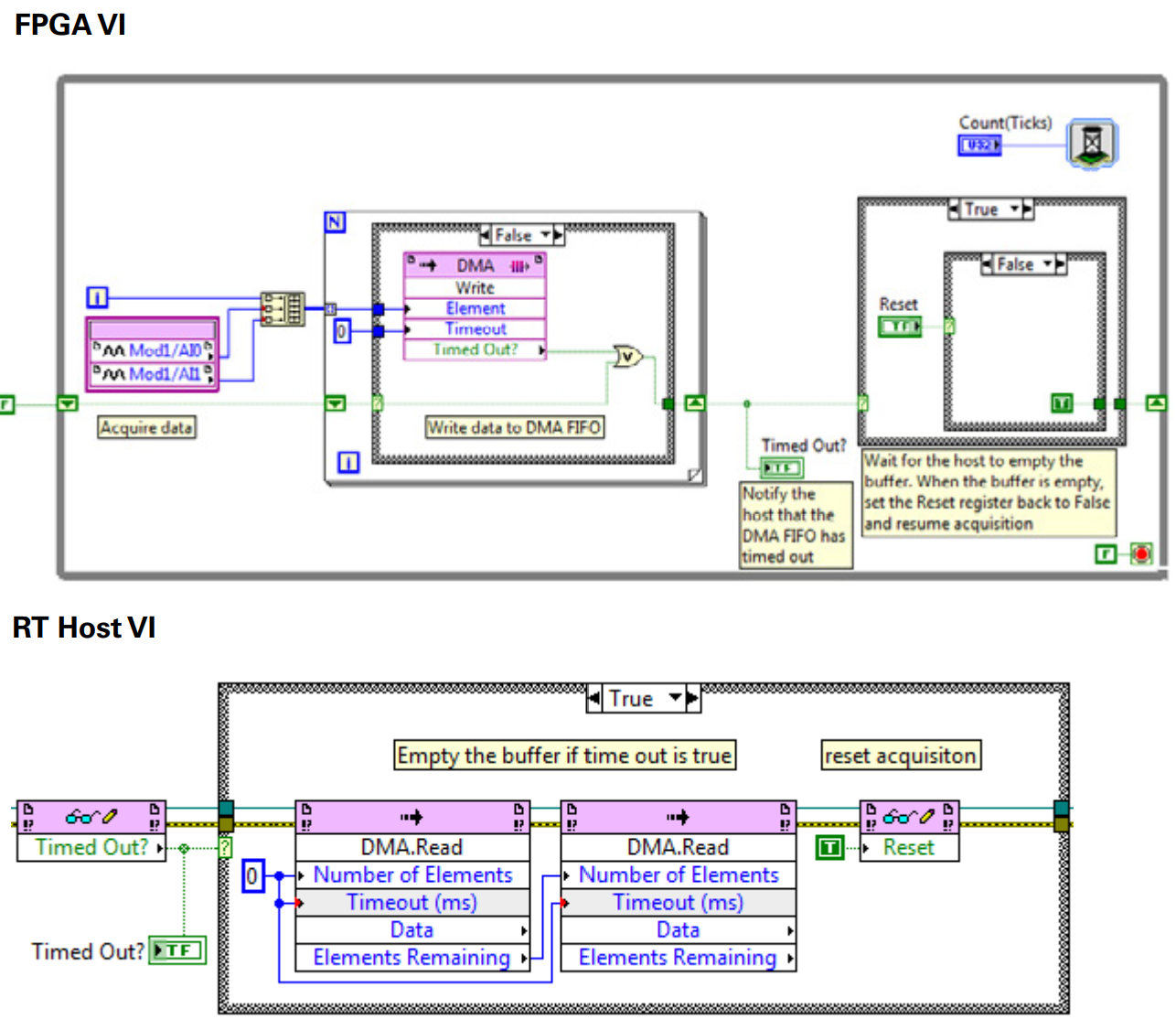

如果无损数据传输很重要,或者如果要将数据从多个I/O通道传输到同一DMA FIFO,则必须能够监控DMA机制的状态并对发生的任何故障做出反应。在FPGADMA写入节点上,超时通常表示DMA缓冲器已满。当它变为真时,应该监视并锁定它。必须从FPGA端执行此操作,因为仅从主机采样此寄存器不足以捕获快速转换。检测到超时事件后,还需要从中恢复。图5.24提供了检测和处理DMA FIFO超时情况的示例。

图5.24.检测溢出并从中恢复

在此图中,DMA FIFO的超时事件在FPGA VI上受到监控。当发生超时事件时,超时寄存器设置为True。一旦超时寄存器设置为True,它被锁存,直到主机VI清除缓冲区并将复位寄存器设置为True。RT主机VI上的超时情况通过读取剩余元素来刷新缓冲区。一旦缓冲器被清除,复位寄存器将设置为true,FPGA VI上的采集将恢复。通过使用这种处理DMAFIFO超时事件的方法,可以检测缓冲区溢出并从中恢复,从而避免因缺少数据点而创建的bug。

避免缓冲区溢出

如果收到缓冲区溢出,则需要增加主机上的DMA FIFO缓冲区大小、在主机上读取更大的缓冲区或在主机上更频繁地读取。请记住,许多控制和监视应用程序只需要最新的数据,因此丢失数据对于系统来说可能不是问题,只要它在调用时返回最新的数据。

如果遇到缓冲区溢出,可以使用DMA配置调用增加主机FIFO缓冲区,如图5.25所示。对于FPGA到RT的传输,经常发生溢出,因为主机FIFO缓冲器(而不是FPGAFIFO缓冲器)不够大。通过FIFO属性页设置的DMAFIFO的大小仅决定占用FPGA内存的FPGAFIFO缓冲区的大小。默认情况下,主机FIFO缓冲区大小为10,000个或FPGAFIFO缓冲区大小的两倍,以较大者为准。

图5.25.增加主机上的DMA FIFO大小

增加缓冲区的大小有助于减少由偶发事件(如总线和主机处理器争用)引起的缓冲区溢出情况。但是,如果平均传输速率高于系统可以承受的速率,则无论缓冲区的大小如何,数据最终都会溢出缓冲区。使用适当大小的缓冲区减少缓冲区溢出情况的一种方法,是尝试一次读取大量数据,这样可以降低每个数据单元的开销,从而提高整体吞吐量。

CompactRIOWaveform Reference Library

如果应用需要使用DMA FIFO来从FPGA传输模拟数据,可以利用NI开发的CompactRIO波形参考库来快速开始应用开发。该参考应用程序介绍了CompactRIO波形数据采集VI和示例源代码,并支持三角积分和SAR(扫描)模块。

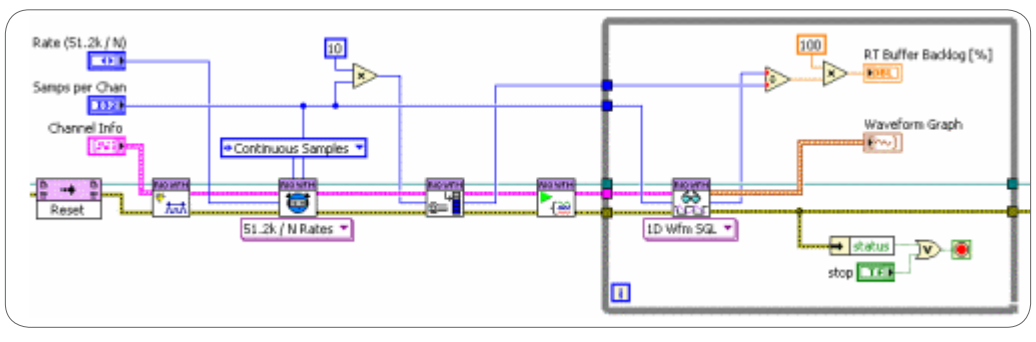

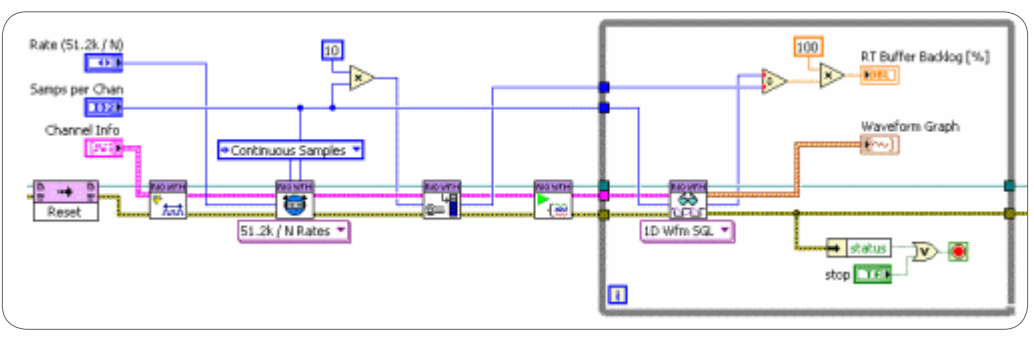

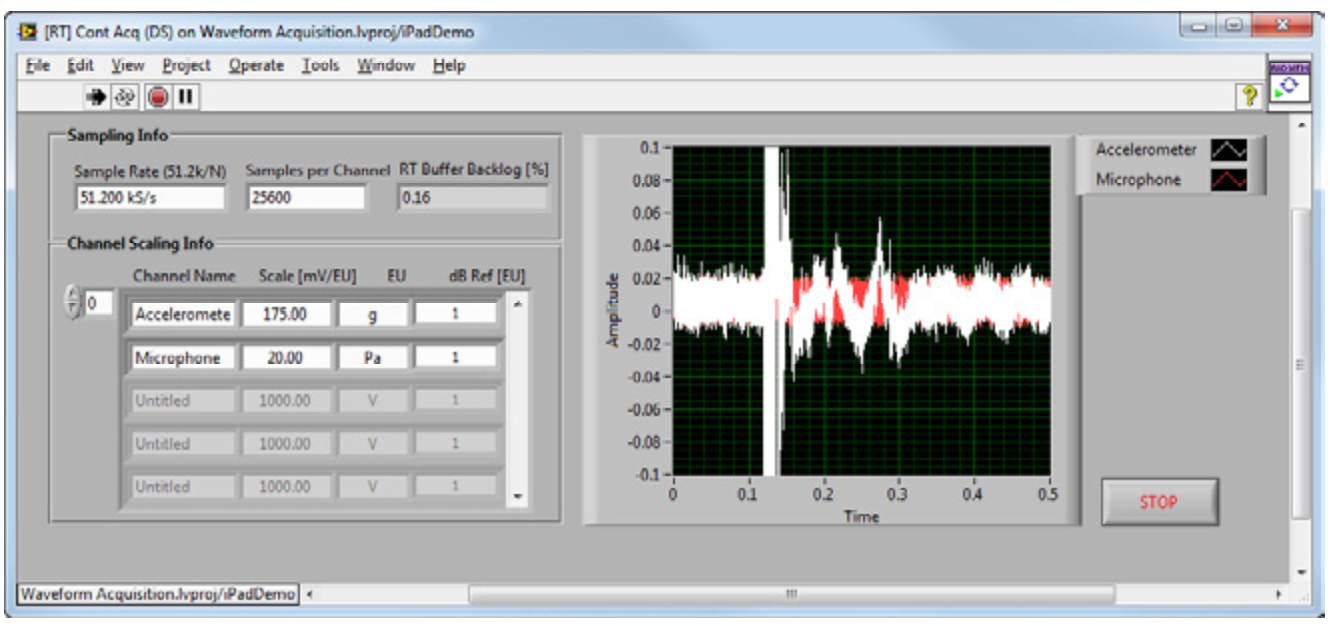

图5.26.使用CompactRIOWaveform参考库API的连续采集

CompactRIO波形参考库包含一个类似NI-DAQmx的API,该API在LabVIEW实时中执行,并将原始模拟数据转换为波形数据类型。波形数据类型使得向UI显示多个I/O通道以及与常见的数据记录API接口(如技术数据管理流(TDMS))变得容易。API还会根据配置的比例将数据转换为适当的工程单位。

图5.27.使用CompactRIO波形参考AP

该库包括一个FPGA VI,需要稍微修改该VI,以参考系统中使用的I/O模块。对于大多数应用,只需要修改FPGA VI。此VI旨在在使用DMA FIFO时提供最佳流性能,包括用于监控和处理缓冲区溢出情况的机制。每当使用DMA FIFO从一个或多个模拟通道流式传输数据时,请使用此FPGA VI模板作为开始。

可以在NI开发人员专区白皮书NICompactRIO波形参考库中找到更多信息包括安装文件。

DeltaSigmaAcquisition.lvpj和SARAcquisition.lvpj在

安装库后可在\Program Files\National Instruments\LabVIEW[Version]\user.lib\cRIOWfm\_exampleProjects中找到。

其他参考资料

■ How DMATransfers Work

■ BestPractices for DMA Applications

有关在FPGA目标上使用DMA FIFO的更多信息,请参阅LabVIEW帮助文档TransferringData Using Direct Memory Access。

通过中断同步FPGA和主机VI

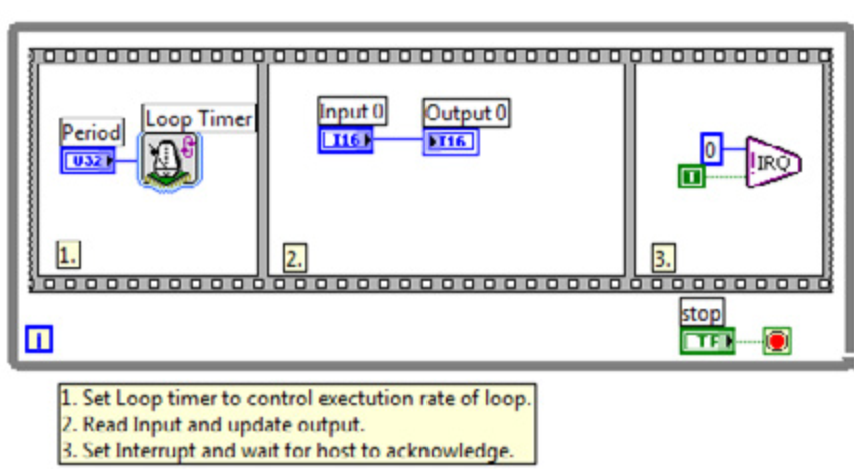

LabVIEW FPGA具有中断,允许主机VI等待FPGA引发指定的中断,从而同步FPGA和主机VI。FPGA VI可以阻塞,直到主机确认中断。这样就无需持续检查FPGA寄存器的状态以查看是否已设置给定标志,并且在未引发中断时降低了CPU使用率。在单核主机上,与轮询和睡眠方法相比,可以实现相对良好的延迟并降低CPU负载。图5.28中的示例显示了如何在FPGA上实现中断。此示例称为同步中断方法,可在NI示例查找器中找到。

图5.28.用于发送中断的LabVIEW FPGA编程结构

中断提供简单的代码和简单的API,但应该注意以下事项:

■处理主机侧的中断通常涉及5μs至50μs的开销。此响应延迟可能是可以接受的,具体取决于应用程序或事件的频率。

■如果不希望FPGA VI在中断被确认之前阻塞,则应添加单独的FPGAloop来发送中断。

■中断不是多核目标上延迟最低的选项。通过专用于CPU内核来持续监控FPGA寄存器(无休眠),可以获得最快的响应时间。

其他参考资料

■ UsingInterrupts on the FPGA to Synchronize the FPGA and Host

■ SynchronizingFPGA VIs and Host VIs Using Interrupts

需要说明的是,上述的例程和文档,都是可以下载的,双击即可打开,其中压缩文件是可以采用粘贴复制的方式,拷贝到硬盘上。这不是图片,各位小伙伴看到后尝试一下,这个问题就不用加微信咨询了。有关LabVIEW编程、LabVIEW开发等相关项目,可联系们。附件中的资料这里无法上传,可去公司网站搜索下载。

楼主最近还看过

- 组态王的点数是怎么计算的

[5592]

[5592] - 请问力控和组态王支持OPC吗?...

[2307]

[2307] - 使用TraceMode开发出来的画面...

[3133]

[3133] - tracemode里说的节点是什么意...

[2264]

[2264] - 组态王总是显示“调色板组件错...

[3874]

[3874] - 求助西门子STEP7 PID调节问题...

[2009]

[2009] - 怎样将WinCC V5.0项目移植到...

[4889]

[4889] - 官方下载:SIMATIC WinCC V7....

[15798]

[15798] - 组态王,怎样制作下拉式选择框...

[2477]

[2477] - 自整定pid算法

[5241]

[5241]

官方公众号

智造工程师

-

客服

客服

-

小程序

小程序

-

公众号

公众号

工控网智造工程师好文精选

工控网智造工程师好文精选