LabVIEWCompactRIO 开发指南31 在LabVIEW FPGA中使用DMA FIFO 点击:377 | 回复:0

LabVIEWCompactRIO 开发指南31

在LabVIEW FPGA中使用DMA FIFO

要为流数据创建DMA缓冲区,请右键单击FPGA目标并选择New...»FIFO。为FIFO结构指定一个描述性名称,并选择“target to host”作为类型。这意味着数据应该通过这个DMA FIFO从FPGA目标流向实时主机。还可以设置数据类型和FPGAFIFO深度。单击确定将这个新的FIFO放入项目中,可以将其拖放到FPGA框图中。

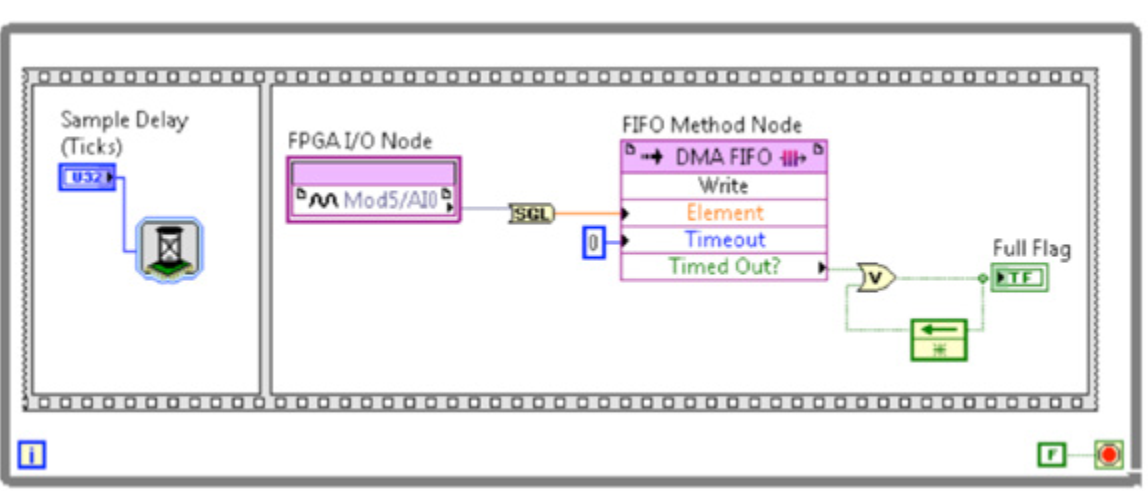

图5.21.一个通道上的简单DMA传输

提示:在LabVIEW2012FPGA及更高版本中,可以将定点数据转换为单精度浮点数据。将这种转换卸载到FPGA可以节省大量处理器资源。对于早期的LabVIEW版本,可以通过可下载的示例或NI开发人员专区文档LabVIEWFixed-Point (FXP) to Single (SGL) Conversion on LabVIEW FPGA.转换来获得类似的转换功能。

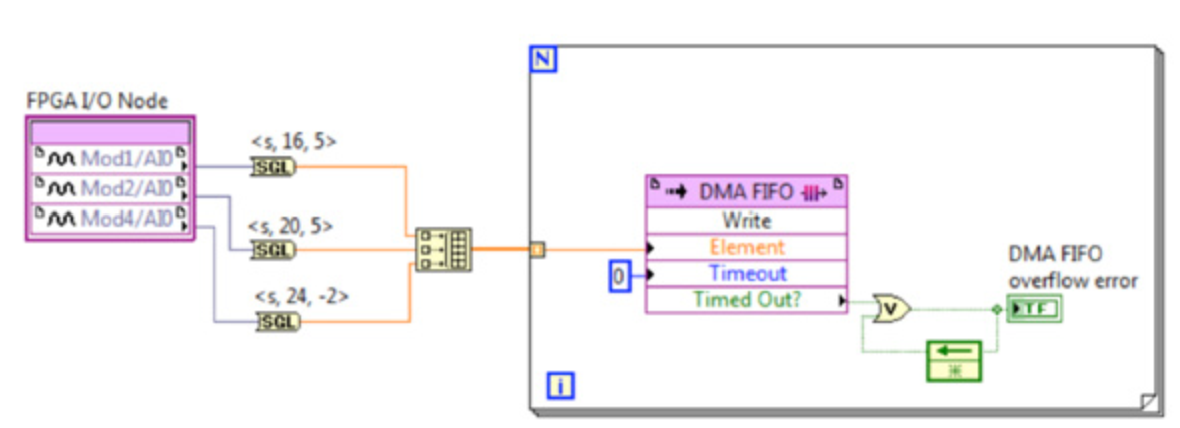

可以使用同一DMA通道传输多个数据流,例如从I/O通道收集的数据流。大多数CompactRIO系统具有三个DMA通道。在混合模式下,CompactRIO系统只有一个DMA通道。要将多个数据流或I/O通道打包到一个DMA FIFO中,请使用图5.22所示的交错技术,并在主机上使用抽取进行解包。

图5.22.在For循环上使用构建数组和索引来实现交错的多通道数据流

将多个模拟输入通道传递到一个DMA FIFO时,通道的存储方式与表5.1所示类似。此表假设四个模拟输入通道交错到一个DMA FIFO中。主机VI上的解包算法期望元素按此特定顺序到达。如果FIFO溢出和元件丢失,则主机VI上的解包算法无法将数据点分配给其不正确的模拟输入通道。因此,从多个模拟输入通道读取数据时,确保无损数据传输非常重要。

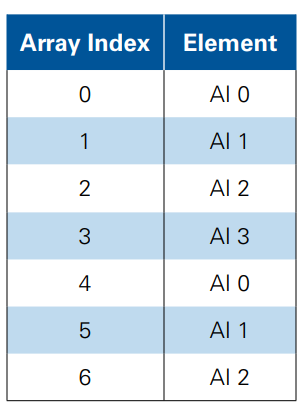

表5.1.将多个通道写入一个DMA FIFO时,主机VI期望element按特定顺序到达

在主机上使用DMA FIFO

通常,在主机VI上专用于一个单独的循环,以使用主机接口节点从DMA缓冲区检索数据。在CompactRIO系统上从DMA FIFO读取数据时,请执行以下三步步骤,以实现最佳性能:

1.将DMA读取超时设置为零。

2.读取固定大小的元素数(数据通道数的倍数)。

3.等到缓冲区已满后再读取元素。

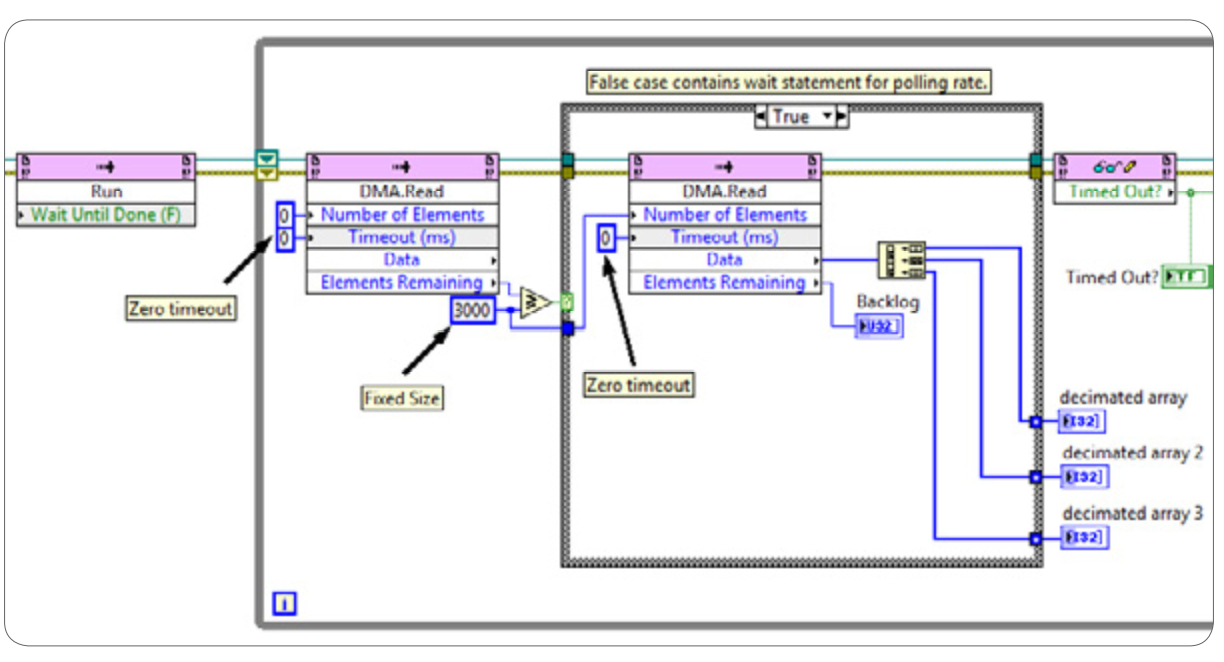

图5.23提供了高效使用DMA FIFO读取函数获取连续I/O数据流的示例。第一个DMAFIFO读取函数计算缓冲区中剩余的元素数,并根据3000个元素的固定大小对其进行检查。如果要传递数据数组,则输入的元素数应始终是数组大小的整数倍。例如,如果要传递一个包含八个元素的数组(如来自八个I/O通道的值),则“Numberof Elements”应为8的整数倍(如80,为每个I/O通道提供10个样本)。

一旦缓冲区达到3000个元素,第二个DMA FIFO读取函数就会读取数据或在False大小写中休眠,并在下一次迭代时再次检查。每个DMA事务都有开销,因此读取较大的数据块通常更好。

最后,使用抽取一维数组函数按通道组织数据。

图5.23.从DMA FIFO读取数据

无论何时从DMA FIFO读取数据,都必须能够检测缓冲区溢出或超时情况并从中恢复,以保持数据正确性。下一节将提供推荐的体系结构,以确保在使用DMA FIFO时进行无损数据传输。

需要说明的是,上述的例程和文档,都是可以下载的,双击即可打开,其中压缩文件是可以采用粘贴复制的方式,拷贝到硬盘上。这不是图片,各位小伙伴看到后尝试一下,这个问题就不用加微信咨询了。有关LabVIEW编程、LabVIEW开发等相关项目,可联系们。附件中的资料这里无法上传,可去公司网站搜索下载。

楼主最近还看过

- UP550中文使用说明书

[3798]

[3798] - sql 2005+wincc62 sp2 asia下...

[3381]

[3381] - 西门子S7-300PLC符号表和变量...

[8133]

[8133] - 组态王如何置位离散量

[2667]

[2667] - 哪位知道OSI软件公司(生产PI...

[3882]

[3882] - 求助:VB与s5-100PLC的通信

[1968]

[1968] - 用单片机自制PLC软件大全

[2573]

[2573] - 分享一个软件-SMC气路图绘制

[13077]

[13077] - RSView用户手册

[3584]

[3584] - 我有三菱GPPW软件有谁需要?

[2462]

[2462]

官方公众号

智造工程师

-

客服

客服

-

小程序

小程序

-

公众号

公众号

工控网智造工程师好文精选

工控网智造工程师好文精选