LabVIEWCompactRIO 开发指南24 第5章通过LabVIEW FPGA定制硬件 点击:80 | 回复:0

LabVIEWCompactRIO 开发指南24

第5章通过LabVIEW FPGA定制硬件

本章将介绍了一些练习,以及使用LabVIEW FPGA模块和CompactRIO开发高性能控制和监测系统的高级技巧和技巧。它介绍了推荐的编程实践、避免常见错误方法以及创建快速、高效且可靠的LabVIEW FPGA应用程序的多种方法。

FPGA技术

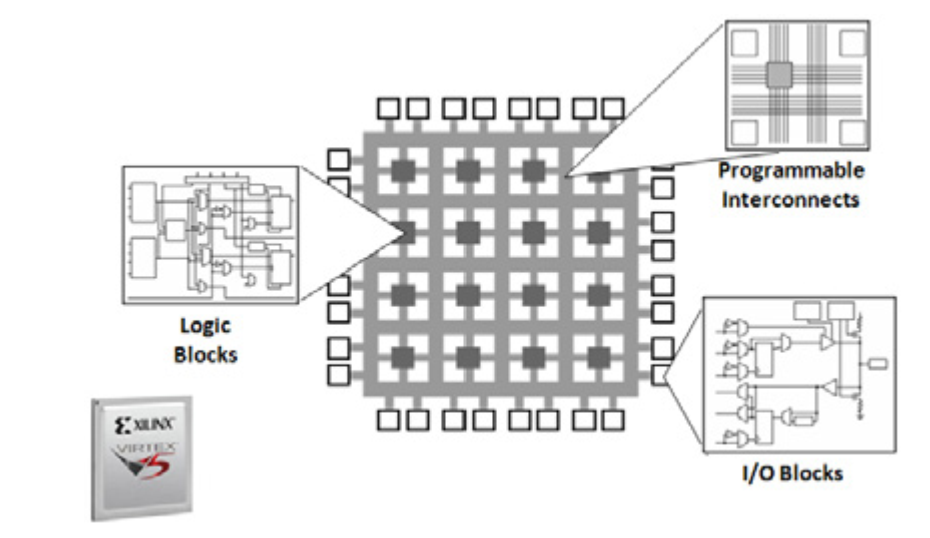

FPGA提供了一个高度并行且可定制的平台,可以使用该平台以硬件速度执行高级处理和控制任务。FPGA是由三个基本组件组成的可编程芯片:逻辑块、可编程互连和I/O块。

图5.1.FPGA由可配置逻辑和I/O模块组成,通过可编程互连连接在一起

逻辑块是数字组件的集合,例如查找表、乘法器和多路复用器,其中处理数字值和信号以生成所需的逻辑输出。这些逻辑块通过可编程互连连接,将信号从一个逻辑块路由到下一个逻辑块。可编程互连还可以将信号路由到I/O模块,以便与周围电路进行双向通信。有关FPGA硬件组件的更多信息,请参阅LabVIEW FPGA帮助文档:FPGA硬件概念简介。

FPGA的时钟速率相对低于CPU和GPU,但它们通过允许创建可在一个时钟周期内执行多个操作的专用电路来弥补时钟速率的差异。结合与NI可重配置I/O(RIO)设备上的I/O紧密集成,可以实现比用处理器解决方案更高的吞吐量和确定性以及更快的响应时间。这有助于我们处理高速流、数字信号处理(DSP)、控制和数字协议应用。

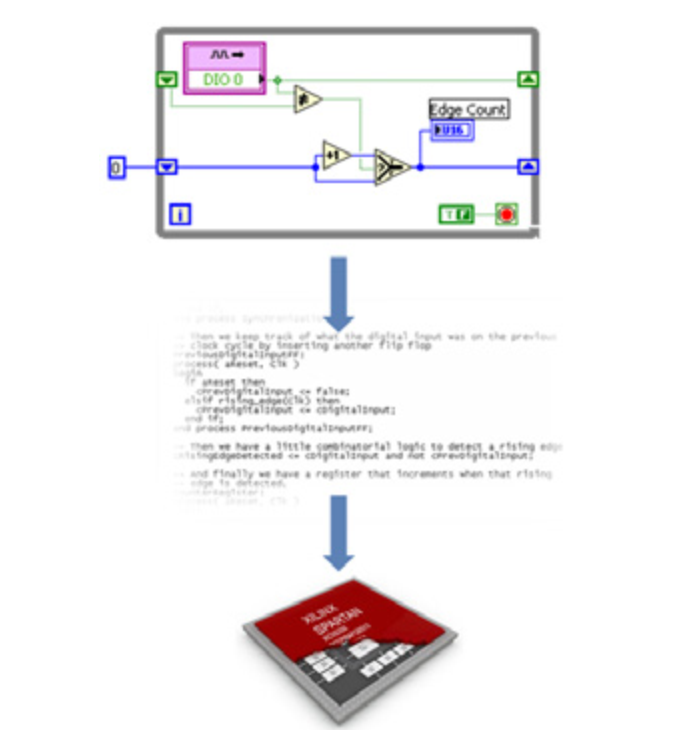

由于LabVIEWFPGAVI是合成到物理硬件,因此FPGA编译过程与传统LabVIEWforWindows或LabVIEW实时应用程序的编译过程不同。为FPGA编写代码时,编写的LabVIEW代码与为其他目标编写的代码相同,但选择运行按钮时,LabVIEW内部会经历不同的过程。首先,LabVIEW FPGA生成VHDL代码,并将其传递给Xilinx编译器。然后,Xilinx编译器合成VHDL,并将所有合成的组件放置并路由到位文件中。最后,将位文件下载到FPGA。此过程比其他LabVIEW编译更复杂,可能需要长达几个小时,具体取决于设计的复杂程度。在本章的后面部分,将了解有关调试和仿真FPGAVI的更多信息,以便可以减少编译频率。

图5.2. LabVIEW FPGA开发流程

建立设计流程

根据LabVIEWFPGA应用程序的复杂性,客户可能希望快速编写程序并编译到硬件,或者可能希望利用内置仿真器来调试、测试和验证代码,而不必在每次进行更改时都编译到硬件。这里介绍了一个推荐设计流程示例,以提高在LabVIEW FPGA中编程时的效率。

1.建立功能和性能要求

2.设计软件架构

3.实现LabVIEW FPGA代码

4.测试和调试LabVIEW FPGA代码

5.优化LabVIEW FPGA代码

6.将LabVIEW FPGA代码编译到硬件

7.部署系统

接下来的几节将介绍此设计流程,从实现LabVIEW FPGA代码开始。前两个主题已在LabVIEWforCompactRIO开发员指南第一部分,简介和基本架构中讨论。

需要说明的是,上述的例程和文档,都是可以下载的,双击即可打开,其中压缩文件是可以采用粘贴复制的方式,拷贝到硬盘上。这不是图片,各位小伙伴看到后尝试一下,这个问题就不用加微信咨询了。有关LabVIEW编程、LabVIEW开发等相关项目,可联系们。附件中的资料这里无法上传,可去公司网站搜索下载。

楼主最近还看过

- wincc报表选择时间间隔

[4875]

[4875] - 用组态王收发短信的最好方法

[2454]

[2454] - 三菱软件大全

[11600]

[11600] - 西门子PLC和安卓APP连接

[7351]

[7351] - 软件问题导致电子图板意外关...

[2966]

[2966] - 工控网中令人厌恶的现象!

[2669]

[2669] - WIN7 安装下 STEP 7 MicroW...

[6843]

[6843] - 如何开发OPC Server(风间月)

[6127]

[6127] - wincc变量记录如何记录字符串...

[2696]

[2696] - 搞工控的交朋友!

[2659]

[2659]

官方公众号

智造工程师

-

客服

客服

-

小程序

小程序

-

公众号

公众号

工控网智造工程师好文精选

工控网智造工程师好文精选