静态SDRAM和动态SDRAM的区别 点击:192 | 回复:0

SDRAM有一个同步接口,在响应控制输入前会等待一个时钟信号,这样就能和计算机的系统总线同步。时钟被用来驱动一个有限状态机,对进入的指令进行管线(Pipeline)操作。这使得SDRAM与没有同步接口的异步DRAM相比,可以有一个更复杂的操作模式。

静态记忆

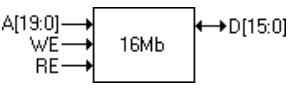

假设我们要将16Mb存储器连接到FPGA。

16Mb表示内存可容纳1600万位(准确地说是16777216位)。现在,很少对比特进行单独寻址,而是通常以8或16的数据包(我们称其为字)进行寻址。因此,如果我们的16Mb存储器被组织为16位的1M字,则需要20位地址总线和16位数据总线,以及一些可写和可读信号。

实际的存储器也将具有CS(片选),如果存储器是同步的,则为时钟(为清晰起见,在图片中将其省略)。

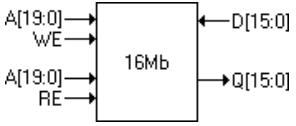

现在,如果该内存是一个Blockram(在FPGA内部),它将看起来有所不同(假设存在如此大的16Mb Blockram ...典型的Blockram要小得多)。

如您所见,它仍然是一块内存,但是有两条地址总线。那是因为现代FPGA中的Blockram是双端口的……这意味着两个代理可以同时访问存储器。通常,一个代理写入内存,而另一个则读取。因此,每个代理的内存都有独立的地址和数据总线。上面的图片在顶部显示了第一个(写)代理,在底部显示了第二个(读)代理。更高级的Blockram允许每个代理读取和写入,但是上面显示的体系结构是最常用的。同样,blockram通常也被同步使用,因此每个代理都必须提供一个时钟(未在图片中显示)。

到目前为止,所显示的内存是静态的,这意味着仅通过对其施加电源即可保存其内容。另外,静态存储器可以看作是一个长字形的线性数组(您只需提供一个地址即可访问匹配的数据...无需复杂)。需要权衡的是每比特成本要比...高得多。

动态记忆

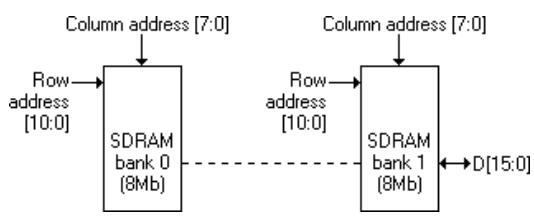

我们将使用SDRAM,它是动态内存(SDRAM中的“ D”)。在动态内存中,内存不被视为单词的长线性数组,而是被组织为单词的矩阵(行/列)。

上图显示行的12位和列的8位,如前所述总共有20个地址位...很容易。

有一种复杂性:为了提高性能,将内存分成相等的块(称为“存储体”)。那是因为某些动态内存操作速度很慢,因此拥有存储体可以在等待另一个存储体的同时使用它。

因此,如果我们的16Mb SDRAM有2个存储区,则每个存储区拥有8Mb。

访问SDRAM时,FPGA必须选择存储体(1位),行(现在只有11位)和列(8位),总共需要20位。但这是一个两步过程:首先是行+库,然后是列:

•FPGA选择一个存储区并激活其行之一。然后它等待几个时钟(等待行准备就绪)。

•现在,该行处于活动状态,FPGA只需提供列地址即可访问(读取和/或写入)该行中所需的任何数据。

•FPGA处理完该行后,必须先关闭该行,然后再打开新行。

为了获得最佳性能,用户(= FPGA)希望避免过多地打开和关闭行,而是在关闭行之前尽可能多地完成工作,并在不同存储体中进行交错操作,以免浪费时钟周期。大多数SDRAM实际上有4或8个存储体,每个存储体都是独立的,因此可以激活自己的行。

楼主最近还看过

- 急!为什么485串口接收不到数...

[1240]

[1240] - TCL- 局部变量和全局变量

[3176]

[3176] - STC单片机的新版ISP协议

[1181]

[1181] - 21control开发板、学习板带给...

[1224]

[1224] - PID

[6875]

[6875] - 用ARM做工业控制怎么样?

[1647]

[1647] - Unix是否可以作为嵌入式系统

[1261]

[1261] - 单片机、DSP和嵌入式

[1006]

[1006] - USB接口产品的快速设计方法

[1210]

[1210] - ZigBee学习之7——OSAL(操作系...

[1201]

[1201]

官方公众号

智造工程师

-

客服

客服

-

小程序

小程序

-

公众号

公众号

工控网智造工程师好文精选

工控网智造工程师好文精选