SRAM灵敏放大器的类型及设计思想 点击:447 | 回复:0

本篇文章内容宇芯电子主要介绍关于SRAM芯片中灵敏放大器的类型以及设计。

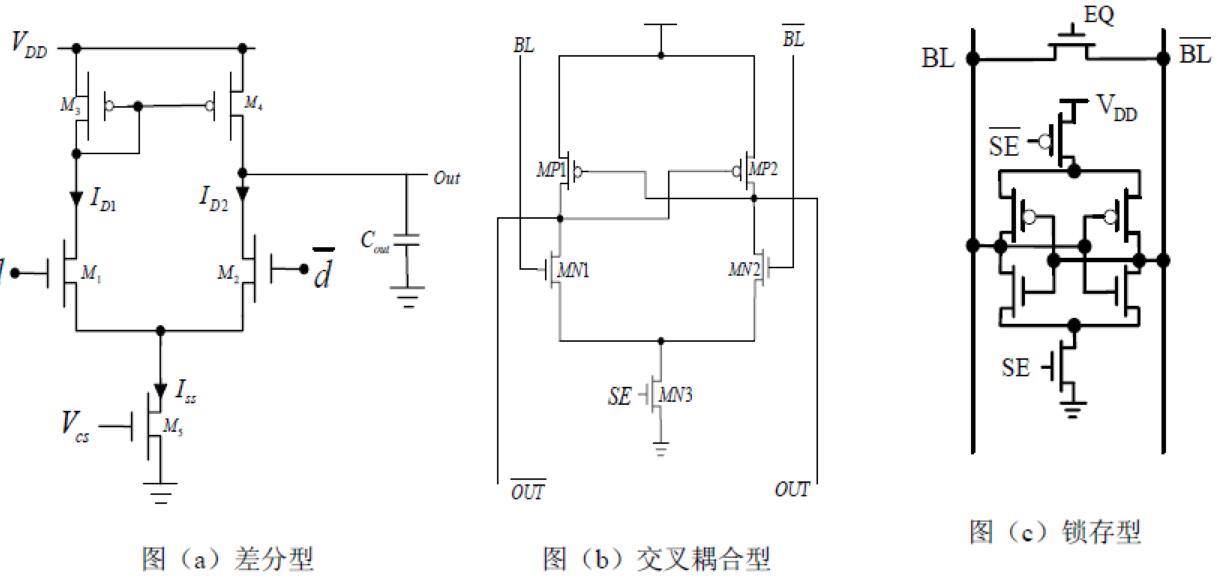

如图1 所示为几种基本灵敏放大器的结构。差分放大器因其具有抗干扰能力强、电压摆幅大、偏置电路简单和线性度高的优点,多用在CMOS

存储器读出放大单元的设计中,如SRAM、DRAM 等。交叉耦合型灵敏放大器具有速度快的特点。

如图(b)所示,交叉耦合放大电路中,由PMOS

管组成的交叉耦合对是由差分结构中的电流镜替代而成的,相对于差分电路而言,正反馈的结构能加快读取速度,然而由于其中的正反馈,使得它容易由于器件尺寸的不匹配而被锁存在一个错误的状态。锁存型灵敏放大器表现在当CMOS

反相器处在它的过渡区时将表现出很高的增益。此时NMOS 和PMOS 管都导通,功耗较大,同时位线负载限制了它的速度。所以该结构一般不应用于SRAM 中。

图1

几种基本灵敏放大器的结构

为了在设计中既能提高存储单元的读取速度,又能增大信号的摆幅,在设计中,我们采用了差分与交叉耦合级联结构。

新型结构灵敏放大器的设计思想

高性能灵敏放大器应对位线电压变化感应灵敏,

当其变化超过10% 时就应输出译码电路选中的存储单元内的值, 同时要求抗干扰能力强, 功耗小。常规的CMOS交叉耦合灵敏放大器对信号的上拉作用强, 下拉作用弱,

无论在电路响应速度、增益还是在输出摆幅上都难以达到要求;而差分结构的灵敏放大电路的直流功耗是相当大的,这些都限制了SRAM

总体性能的提高。

在已有的sram芯片改进方案的基础上,

设计中给出了一种如图1所示的改进后的灵敏放大器电路结构。该电路在设计上采用时钟控制的灵敏放大器,它仅仅在激活的时候产生功耗,但是需要一个时序控制链以便在正确的时间激活。并且采用两级串联结构。第一级采用交叉耦合结构,便于提高响应速度,

第二级采用差分结构,便于提高增益,抗干扰能力强(共模信号的抑制作用较大)。 两级之间的工作通过buffer控制。

楼主最近还看过

- 跪求51单片机与固态继电器的...

[2557]

[2557] - 求助:HEX文件转c文件

[1297]

[1297] - 求助 嵌入式WINCE如何增加中...

[2306]

[2306] - 3G嵌入式软件开发 的就业前景...

[1232]

[1232] - 关于远距离数据采集的方案

[2940]

[2940] - 大连做嵌入式的到此交流

[1061]

[1061] - MCGS嵌入式组态软件面市--华...

[1248]

[1248] - 未来会用嵌入式板卡代替PLC中...

[981]

[981] - S3C44B0全套388元

[1406]

[1406] - 致单片机初学者

[1145]

[1145]

官方公众号

智造工程师

-

客服

客服

-

小程序

小程序

-

公众号

公众号

工控网智造工程师好文精选

工控网智造工程师好文精选