SIS CPU工作原理分析 点击:1287 | 回复:2

楼主最近还看过

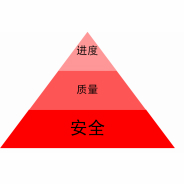

对于传统的SIS系统而言,过于看重CPU的表决功能。

例如HIMA的 H41Q/H51Q, 本质是 2oo2D系统的冗余。

分2个CPU模块,每个模块上2个CPU芯片, 这2个CPU芯片做2取2表决。

任意一个CPU芯片故障,或者2个CPU的运算结果不一致,

就会把整个CPU单元切除掉,用另外一个备份的CPU单元来执行。

另外一个CPU单元也是执行 2取2的表决逻辑。

本质上来说,Honeywell的SM,横河的Prosafe-RS 都是如此。

这就是所谓的四重化容错,--QMR。

本意并不是任何2个CPU就可以进行表决的。

IEC61508 V2的规约中 强调了, CPU不应采用冗余技术来达到相应的安全等级。

冗余就是冗余,冗余是增强系统的可用性,和系统的安全性,安全等级无关。

这句话讲的,我也不知道是针对谁家的。

但是以 ICS的AAdvance为例。

其单CPU时,安全等级只能到SIL2, 采用双CPU表决时(注意此时不同于DCS常规的1:1冗余热备,而是2取2的表决),安全等级可以达到SIL3.

但是此时是2取2表决。 只要有一个CPU失效,就不能达到2取2的效果,就降级为SIL2了。

所以,AAdvance最标准的配置 其实是 2oo3.

3取2表决。 AAdvance 在2oo3 时安全等级为SIL3; 当一个CPU失效时,变为2oo2,安全等级还是SIL3. 再有一个CPU失效,安全等级降为SIL2 或者直接停车。

这就是常说的 3-2-0 安全等级降级处理。

而如 西门子的400FH,HIMA的H41Q/H51Q, Honeywell 的SM等。

其单CPU(单CPU模块单元) 就已经达到了SIL3的安全等级,

所以CPU冗余配置,只是增强系统可用性。

系统的安全等级并不会随着 采用冗余技术而提升。

这也是 规约还强调的,系统的安全等级不应因采用冗余技术而提高,因冗余失效而降低。

举一个很典型的负面例子,就是Siemens-Moore的 QuardLog。

QuardLog的 单CPU时,安全等级只能达到SIL2.

如果要达到SIL3的安全等级,必须配置2个CPU,且必须进行架对架冗余。

2个CPU插在同一个机架上,都不能实现SIL3的安全等级。

那么这个时候,QuardLog的 安全等级就是采用了CPU冗余技术来实现的,

如果有一个CPU失效,则其安全等级就会降级为SIL2.

这对系统而言,其实是很不安全的。

对于绝大部分的QMR系统而言。

损坏任意一个CPU芯片,或者CPU单元。

都不会导致 程序逻辑出错。

- ABB待遇如何啊?

[9227]

[9227] - 几个出名的控制系统介绍

[4513]

[4513] - DEH液压系统原理一

[3261]

[3261] - P+F安全栅KCD2-STC-1使用指南...

[3628]

[3628] - honeywell tps系统资料谁要

[1996]

[1996] - 中国国产的DCS又少了一家呀,...

[11282]

[11282] - 请问:ABB员工收入?

[2466]

[2466] - 浙大优稳UW500 DCS资料

[3523]

[3523] - Experion PKS 系统 流程图组...

[2683]

[2683] - 自动化改造方案1

[4273]

[4273]

官方公众号

智造工程师

-

客服

客服

-

小程序

小程序

-

公众号

公众号

工控网智造工程师好文精选

工控网智造工程师好文精选