LabVIEW开发FPGA方法与FIFO数据丢失处理 点击:244 | 回复:0

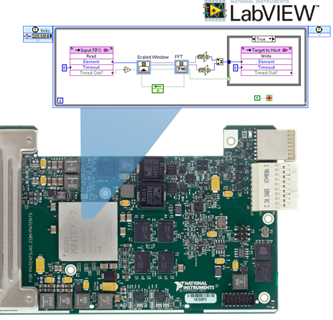

开发基于NI 7975R FPGA的系统涉及一系列流程,包括驱动安装、LabVIEW项目设置、开发调试、编译和与Windows系统的通信。重点在于FIFO的正确配置,避免数据丢失是关键环节之一,尤其是在使用高速数据流传输时。以下将详细介绍这些过程,并重点讨论FIFO数据丢失的原因与解决方案。

FPGA开发流程

驱动安装与工具准备:开发FPGA需要安装LabVIEW FPGA模块以及NI RIO驱动程序。这些工具支持NI 7975R FPGA的编译、调试与通信。确保安装最新版本的NI-RIO驱动程序,兼容LabVIEW和FPGA硬件。

LabVIEW项目创建:在LabVIEW中,创建FPGA项目并选择NI 7975R作为目标设备。项目中包含FPGA VI(虚拟仪器)以及主机VI。FPGA VI执行FPGA上的实时控制和数据处理,而主机VI运行于Windows上,负责数据传输和系统控制。

开发与调试:FPGA开发通常通过LabVIEW图形编程环境进行。编写FPGA代码时,需要使用同步控制、时钟配置和FIFO缓存来管理数据流。在开发过程中,LabVIEW提供了模拟调试工具,可以在不编译FPGA代码的情况下进行调试。

编译与部署:一旦代码编写完成,FPGA VI需要通过编译生成比特流文件并部署到硬件。FPGA编译时间较长,但LabVIEW会在后台完成此过程。编译完成后,系统可以直接加载到硬件中运行。

与Windows通信:FPGA与Windows主机之间的通信可以通过DMA FIFO或直接内存访问(DMA)方式实现。这允许高吞吐量的数据传输,适合实时监控和控制系统。

FIFO数据丢失问题

在高吞吐量应用中,使用FIFO进行数据传输时,可能会遇到数据丢失问题。其原因主要包括FIFO缓存溢出或写/读速率不匹配。以下是常见问题和解决方案:

FIFO溢出:如果FPGA写入FIFO的速度快于主机读取的速度,FIFO缓存可能会溢出,从而导致数据丢失。这在高速数据采集系统中尤为常见,例如信号采集或实时图像处理。

解决方案:

增加FIFO的深度,确保在短时间内存储更多数据(

)。

使用DMA传输大块数据,减少系统对主机CPU的依赖,同时避免高频率的数据读取(

)。

监控FIFO的溢出状态,通过控制逻辑调整数据写入和读取的速率,避免溢出。

读/写速率不匹配:如果主机和FPGA之间的读写速率不匹配,也可能会导致FIFO数据丢失。为了解决这个问题,可以使用同步触发器来协调数据的读写操作。

解决方案:

使用双向FIFO通道,一边读取数据一边写入数据,并设置合适的控制逻辑来平衡读写速率(

)。

定期刷新FIFO,确保不会因为系统卡顿而导致数据堆积(

)。

FPGA DMA FIFO设置问题:DMA FIFO在用于高速数据流时,有时会因为FIFO深度配置不当而导致数据丢失。确保FIFO的深度和DMA传输的块大小相匹配。

解决方案:

设置合适的FIFO缓存深度,根据实际数据传输量调整深度。

确保主机侧能及时处理传输的数据,减少主机处理延迟(

)。

通过适当的设计和FIFO管理,数据丢失问题可以得到有效控制,确保FPGA系统的稳定性和可靠性。

官方公众号

智造工程师

-

客服

客服

-

小程序

小程序

-

公众号

公众号

工控网智造工程师好文精选

工控网智造工程师好文精选