LabVIEWCompactRIO 开发指南第六章40 模块分类 点击:138 | 回复:0

模块分类

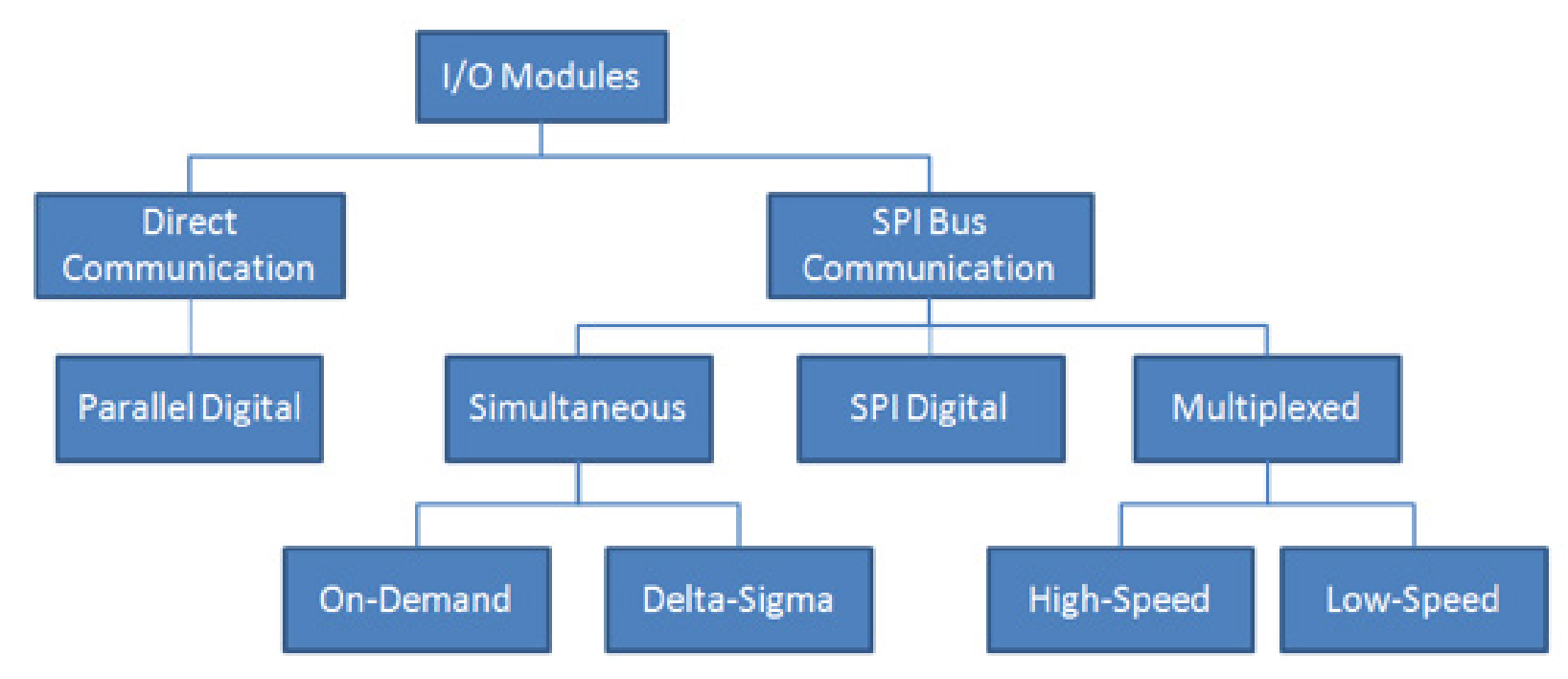

本节介绍不同类型的C系列I/O模块。需要了解这些模块是如何设计以正确实现计时和同步的。模块分类的基本类型如图6.6所示。

图6.6.C系列模块分类组织树

直接FPGA通信

在CompactRIO机箱中与FPGA直接通信的模块,将来自模块前部I/O连接器的信号通过模块背面的15针D-SUB路由到FPGA。这种架构使得使用直接FPGA通信模块进行编程变得更加容易,因为可以将每条线路视为一个唯一的编程实体。唯一使用直接FPGA通信的模块是具有8条或更少线路的数字I/O(DIO)模块。

并行数字

由于直接FPGA通信模块上的每条数字线都编程为一个单独的实体,因此具有八个或更少通道的数字模块也称为并行数字模块。这些模块的并行设计使得其最容易在LabVIEW中编程。并行数字模块的I/O节点可以从SCTL调用,这使得编程更加高效,并且可以从单独的环路同时调用单个通道线,如图6.7所示,无需担心仲裁。

图6.7.可以从单独的环路调用同一并行数字模块上的线路

请注意,在8通道并行模块的DIO线路上的任何时间要求改变方向都会导致中断,必须在LabVIEW框图上适当地处理该中断,以防止在方向改变时使用的其他线路出现毛刺或抖动。NI9402没有这个问题。四条线用于DIO,其他四条线用于控制方向。方向更改可以独立于数据传输发生。NI9401是最广流行的DIO模块之一,使用所有八条DIO线,并且必须切换模式来通信线路状态。此模式更改会影响所有DIO线路,无论哪些线路正在更改状态。

SPI总线通信

串行外设接口总线(SPI)是一种标准的4线通信协议,用于主/从、全双工(双向同时)通信。总线时钟速率通常为1MHz至70MHz。CompactRIO硬件用于与C系列模块通信的SPI时钟速率各不相同,但通常工作在10MHz左右。

SPI总线模块的通用架构包含一个复杂的可编程逻辑器件(CPLD),该器件在模块侧控制ADC/DAC芯片的时序和数据收集。在机箱侧,CPLD通过SPI总线与FPGA通信。根据使用的特定模块和插槽位置,LabVIEWAPI知道如何以及在何处与模块上各个CPLD进行通信。这就是新版LabVIEW中增加新模块支持的原因。

SPI总线挑战

无论前端电路如何,每个SPI模块都通过一条专用SPI总线与CompactRIO机箱中的FPGA通信。这意味着,即使可以并行执行到模块的命令(来自LabVIEW框图上的多个环路)或数据检索(来自具有多个ADC的模块),但这些命令必须通过单个SPI总线进行隔行处理。LabVIEW和NI-RIO驱动程序可以正确地优先处理同时传入的多个呼叫,但如果一个呼叫在前一个呼叫仍在处理时传入,则可能会在控制或数据采集循环中引入不需要的抖动。传达这一概念的另一种方式是,从LabVIEW FPGA程序的不同部分对单个模块的I/O节点调用会产生“硬件竞争条件”。这绝不会限制模块或CompactRIO系统的能力,但需要在程序内仲裁I/O节点调用。执行此操作的最简单方法是将所有I/O节点调用保留在同一循环中,但也可以使用序列结构或信号量。可以在NI开发人员专区文档LabVIEW FPGA的信号量参考设计中找到LabVIEW FPGA信号实现的参考设计。

在继续阅读有关模块的不同分类的信息时,请注意,所有使用SPI通信的模块都必须遵守相同的硬件仲裁警告。

需要说明的是,上述的例程和文档,都是可以下载的,双击即可打开,其中压缩文件是可以采用粘贴复制的方式,拷贝到硬盘上。这不是图片,各位小伙伴看到后尝试一下,这个问题就不用加微信咨询了。有关LabVIEW编程、LabVIEW开发等相关项目,可联系们。附件中的资料这里无法上传,可去公司网站搜索下载。

楼主最近还看过

- 创联天工推出天工组态5.5通用...

[3167]

[3167] - 西门子Insight3.4软件

[2292]

[2292] - 画电气原理图用什么软件好用...

[16929]

[16929] - 请问哪一种组态软件可以编译...

[2023]

[2023] - 各位朋友,现实中实际问题拿来...

[3523]

[3523] - 组态王怎么连接海康威视摄像...

[3910]

[3910] - 智创强档推出新顶级.hk域名首...

[2117]

[2117] - wincc输入输出域如何输入负数...

[3055]

[3055] - 免费索取TRACE MODE6无限点免...

[3686]

[3686] - 浅谈组态软件的现状与发展

[4911]

[4911]

官方公众号

智造工程师

-

客服

客服

-

小程序

小程序

-

公众号

公众号

工控网智造工程师好文精选

工控网智造工程师好文精选