不同类别存储器基本原理 点击:189 | 回复:2

存储器是用来存储程序和各种数据信息的记忆部件。存储器可分为主存储器(简称主存或内存)和辅助存储器(简称辅存或外存)两大类。和CPU直接交换信息的是主存。主存的工作方式是按存储单元的地址存放或读取各类信息,统称访问存储器。计算机的存储器可分成内存储器和外存储器。内存储器在程序执行期间被计算机频繁地使用,并且在一个指令周期期间是可直接访问的。外存储器要求计算机从一个外贮藏装置例如磁带或磁盘中读取信息。

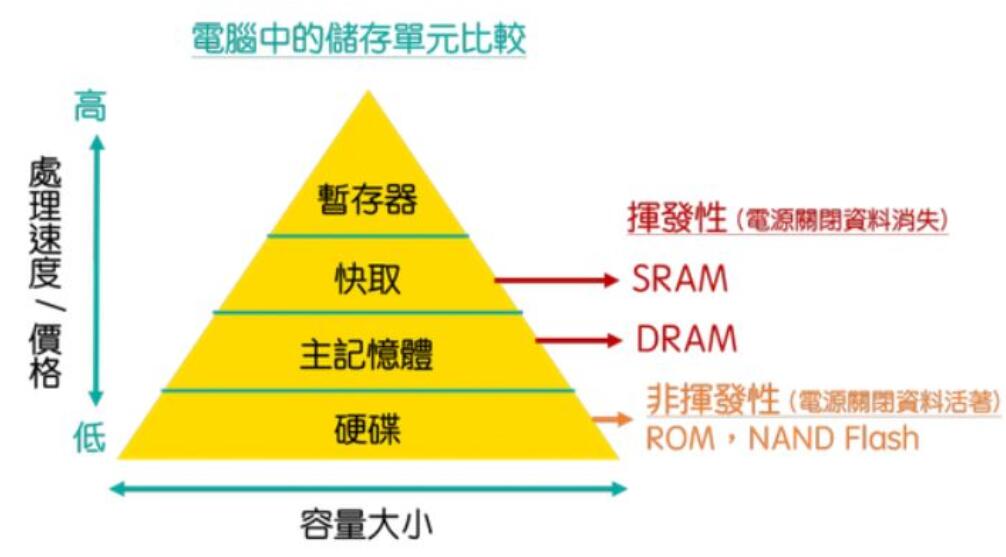

存储器分为易失性存储器和非易失性存储器。易失性存储器分SRAM和DRAM;非易失性存储器以Nor-flash和Nand-flash为典型代表。

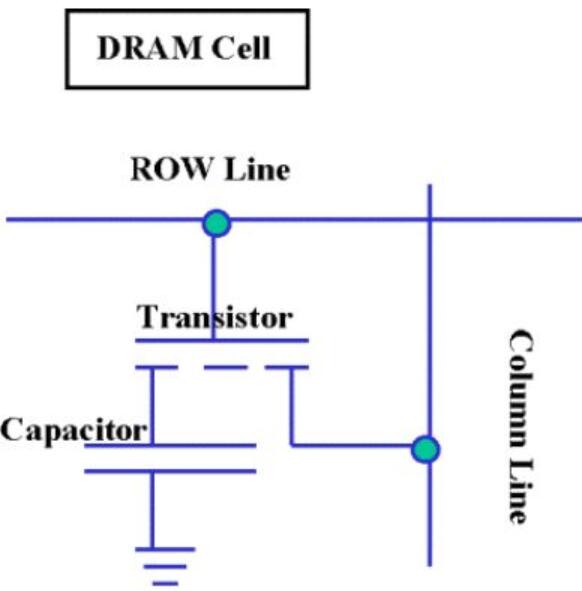

DRAM

DRAM cell结构由1个MOS和1个电容组成,由电容是否带电荷来区分0和1。不过,由于电容漏电流的原因,DRAM无法长时间保存数据,需要“动态”刷新(刷新周期在亚ms级别)。

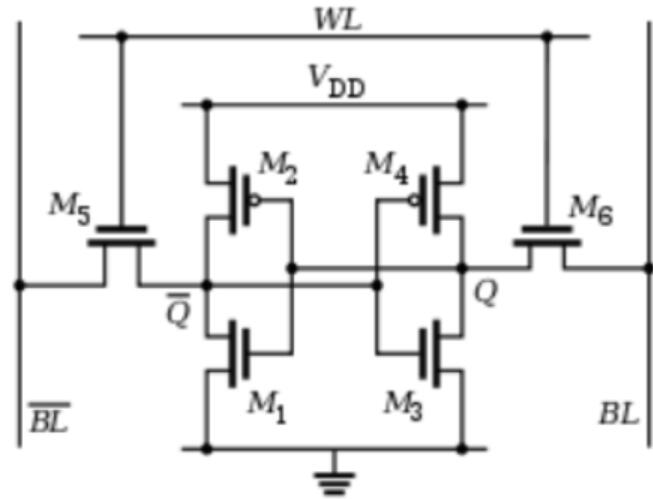

SRAM

SRAM cell有多种不同结构,下图为6个MOS组成的SRAM cell。M1/M2、M3/M4分别为2个反相器,在供电情形下可以锁住0/1信息,不需动态刷新。

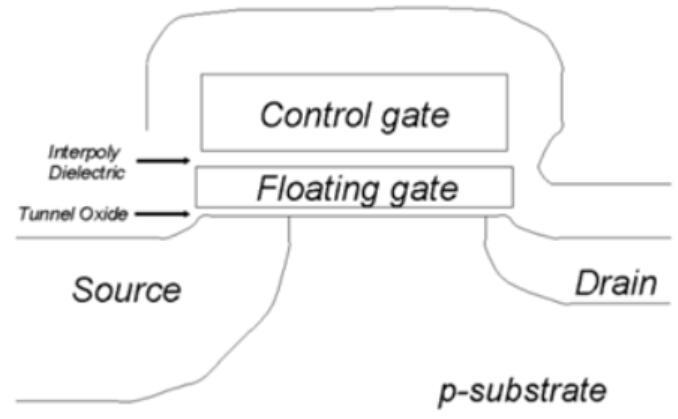

Flash

不管是Nor-flash还是Nand Flash,单位cell的结构都类似如下,为双gate的MOS结构。中间一层floating gate无漏电存在,可以保存住电荷而实现非易失。

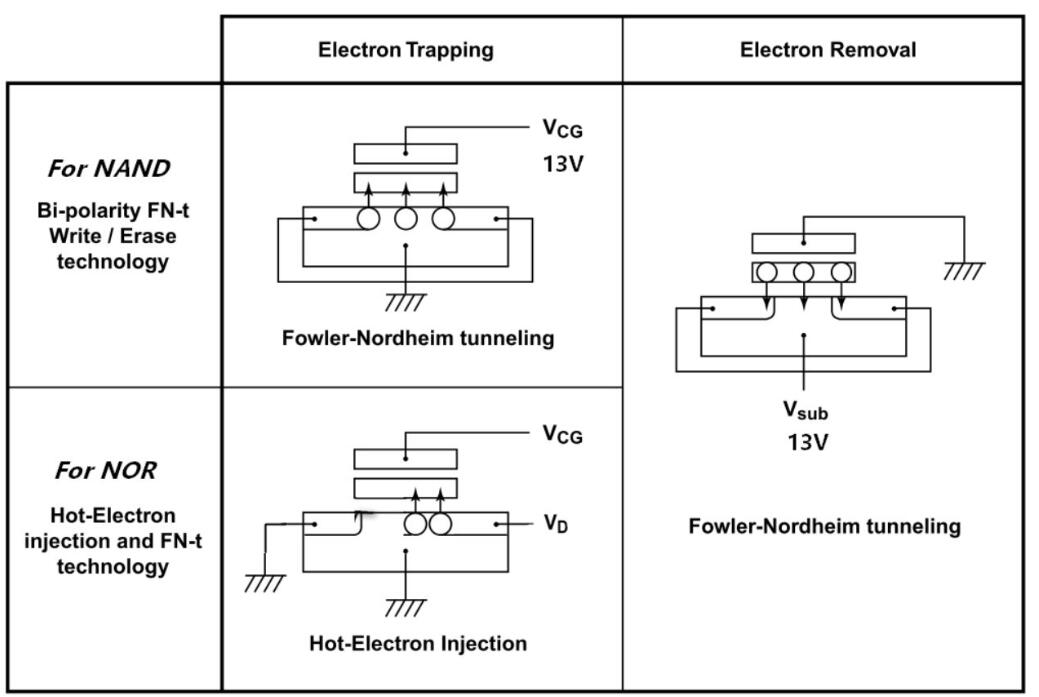

Floating gate上电荷转移需要外加电压实现。在Control gate和沟道之间施加的反向电压可以去除电荷,也即擦除erase操作。在Control gate和沟道或source 之间施加正向电压可以将电荷转移到floating gate上。

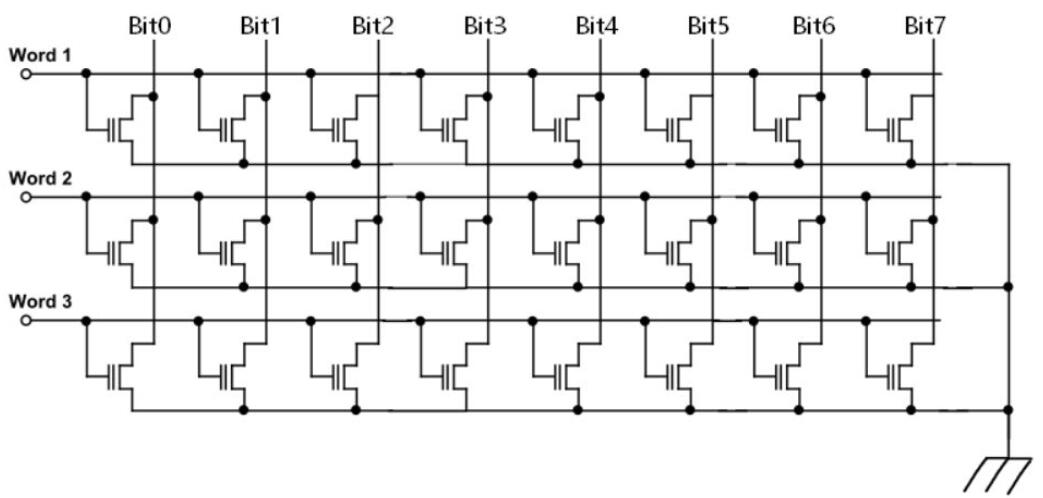

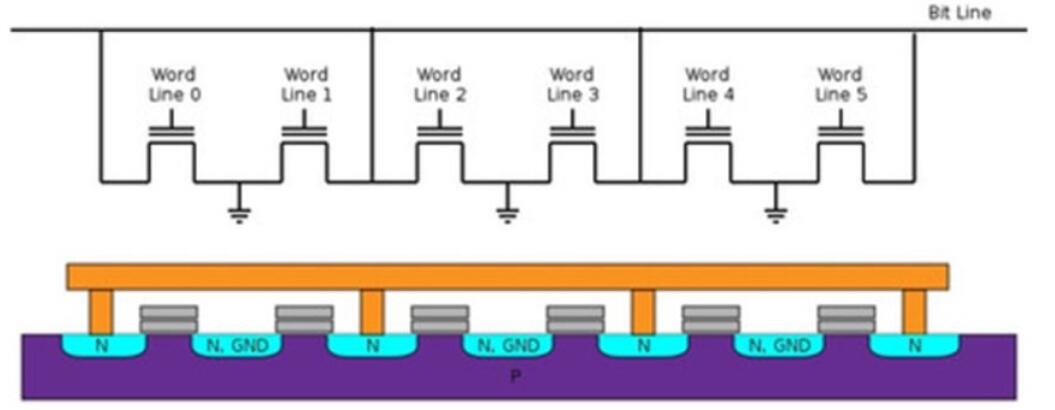

NOR FLASH的结构和特性

通过NOR FLASH的结构原理图,可见每个Bit Line下的基本存储单元是并联的,当某个Word Line被选中后,就可以实现对该Word的读取,也就是可以实现位读取(即Random Access),且具有较高的读取速率。

(1)基本存储单元的并联结构决定了金属导线占用很大的面积,因此NOR FLASH的存储密度较低,无法适用于需要大容量存储的应用场合,即适用于code-storage,不适用于data-storage。

(2)基本存储单元的并联结构决定了NOR FLASH具有存储单元可独立寻址且读取效率高的特性,因此适用于code-storage,且程序可以直接在NOR 中运行(即具有RAM的特性)。

(3)NOR FLASH写入采用了热电子注入方式,效率较低,因此NOR写入速率较低,不适用于频繁擦除/写入场合。

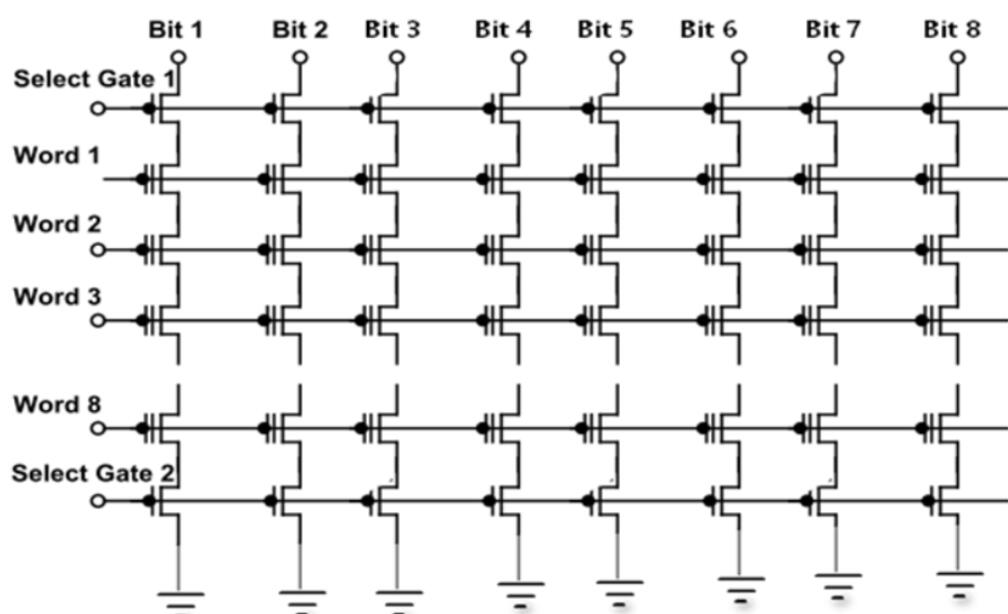

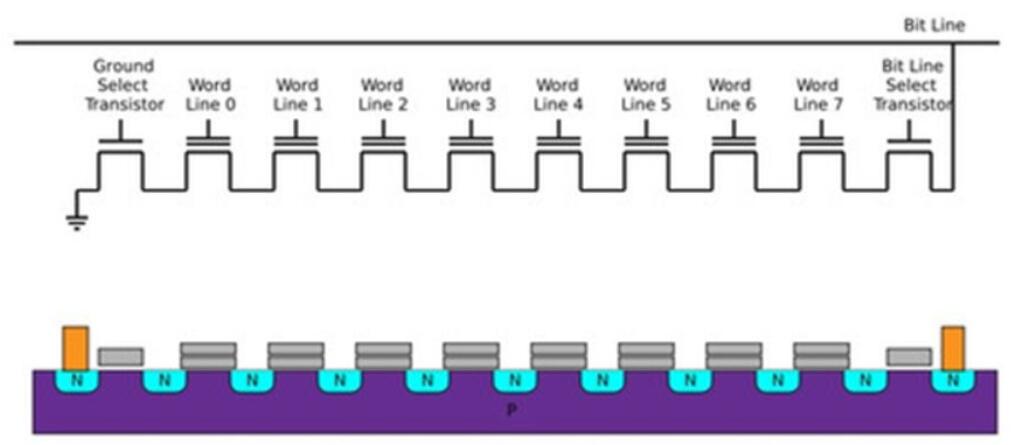

NAND FLASH的结构和特性

通过NAND FLASH的结构原理图,可见每个Bit Line下的基本存储单元是串联的,NAND读取数据的单位是Page,当需要读取某个Page时,FLASH 控制器就不在这个Page的Word Line施加电压,而对其他所有Page的Word Line施加电压(电压值不能改变Floating Gate中电荷数量),让这些Page的所有基本存储单元的D和S导通,而我们要读取的Page的基本存储单元的D和S的导通/关断状态则取决于Floating Gate是否有电荷,有电荷时,Bit Line读出‘0’,无电荷Bit Line读出‘1’,实现了Page数据的读出,可见NAND无法实现位读取(即Random Access),程序代码也就无法在NAND上运行。

基本存储单元的串联结构减少了金属导线占用的面积,Die的利用率很高,因此NAND FLASH存储密度高,单bit成本低。适用于需要大容量存储的应用场合,即适用于data-storage。

不同类别存储器在PC系统中的位置

从单bit成本来看:NAND<NOR<DRAM<SRAM

从读取速度来看:NAND<NOR<DRAM<SRAM

楼主最近还看过

- 谁需要CoDeSys编程说明书

[3404]

[3404] - 电流控制器件和电压控制器件

[3555]

[3555] - 最新版本DSP5509A+CYCLONE I...

[1393]

[1393] - 动手画了ST-link-ii的原理图

[2918]

[2918] - 请问知道PC104专用电源JMM-5...

[1145]

[1145] - “松下PLC ”通过Modem与上位机...

[1558]

[1558] - ARM培训班,手把手教你你也是...

[997]

[997] - 有需要vxworks的么?

[990]

[990] - Visual Studio 2005 在 WinC...

[1747]

[1747] - 谁用过AD7731,讲讲

[1408]

[1408]

官方公众号

智造工程师

-

客服

客服

-

小程序

小程序

-

公众号

公众号

工控网智造工程师好文精选

工控网智造工程师好文精选