软件无线电综合开发平台 点击:431 | 回复:0

北京研创达科技软件无线电综合开发平台

一、概述

为了满足软件无线电验证需要了,设计一块高速板卡板卡,该板卡含2路500MSPS ADC及3路500MSPS DAC,以及支持DDR3、SRIO存储,带485通信接口,千兆网通信接口,支持X86技术。

二、主要技术指标

l FPGA:XC7K410T-2FFG900i

XC7K410T-2FFG900i 3片级联

406720逻辑单元,63550Slices,16个GTX

l ADC:AD9648

采样频率:500MSPS

采样精度:14位

通道数:2通道

集成下变频器

集成NCO

l DAC:AD9142A

播放频率:500MSPS

采样精度:16位

通道数:6通道

集成上变频器

集成NCO

l DDS:AD9912

输出频率:1M-1000Hz

输出幅度:0~-50dB

l FPGA高速互联:

互联协议:SRIO

带宽:SRIO X4

互联速度:1GB/S

l FMC扩展:

3组标准FMC扩展

支持Bank电压调整

l 网络:

支持FPGA自主TCP/IP千兆网通信

l X86处理器:

处理器:Intel E3845

硬盘:128GB

内存:2GB

显示:HDMI

U口:2个

网络:千兆网

l 算法支持:

模拟调制功能:AM/FM/PM

数字调制功能:BPSK、QPSK、8PSK、16QAM、32QAM、64QAM、128QAM、256QAM、MSK、GMSK、2FSK

三、框图及实物

框图:

实物:

四、方案介绍

4.1 ADC部分:

数模转换器ADC拟选用ADI公司的AD9684,该转换器支持4、500MSPS采样频率,14bit精度,双路,接口为并行lvds。

4.2 DAC部分:

模数转换器拟选用ADI公司的AD9142A,该芯片AD9142A是一款双通道、16位、高动态范围数模转换器(DAC),提供1600 MSPS采样速率,可以产生最高达奈奎斯特频率的多载波。

下面是该芯片内部框图:

4.3 FPGA部分

FPGA拟选用Xilinx公司的XC7K410T-2FFG900i作为主控芯片,该芯片资源、速度、功耗都比较理想。

4.4 DDR3

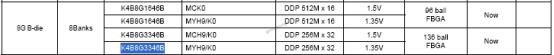

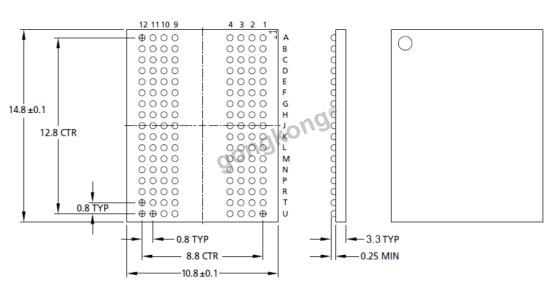

DDR3采用三星公司的K4B8G3346B,该芯片容量为1GB,32位宽,单芯片解决方案,是非常理想的存储颗粒。

4.5 时钟合成器

时钟合成器拟选用AD9528,该芯片能够输出12路10M-1000M频率,可以满足本项目使用需要。

4.6 千兆网接口

通过88E1111,作为一个千兆phy芯片,支持GMII/SGMII/1000Base+协议。本方案中,用Verilog实现一个TCP/IP服务器,计算机可以通过RJ45连接到FPGA上,实现寄存器读写及FIFO读写操作,传输速度可以达到60MB/s。

4.7 串口接口

串口接口芯片拟选用MAX3162,该芯片支持RS232、RS485、RS422协议,且可以方便切换非常方便。

4.8 FMC扩展接口

扩展接口拟选用行业上比较成熟的FMC_LPC接口,IO数为可以达到38对LVDS,该连接器支持差分接口,传输速度支持到10GHz,且高密度、高可靠性,是比较理想外扩方案。

4.9 DDS芯片:

DDS芯片选用AD9912,该款芯片可以实现1M-1000Hz的频率输出。

五、交付内容

开发平台:Xilinx FPGA平台

交付内容:板卡1套及全套源代码

FPGA源代码含:AD、DA、DDR、GTP、SRIO、UART、RJ45、DDS。

上位机源代码:VC6.0

- 三极管9012管脚图参数与应用...

[7922]

[7922] - 有没有线缆方式传输10公里的...

[902]

[902] - 电磁阀接线时为什么要并联一...

[4990]

[4990] - FX0s-14MR里面的驱动芯片TD6...

[1677]

[1677] - 求三菱1302H02集成电路

[1150]

[1150] - 急!!!三极管型号问题

[1337]

[1337] - 三菱人机FX30DU-E液晶屏出现...

[950]

[950] - 直流接触器线圈并联多大的二...

[971]

[971] - 求助:谁能提供西门子OP17液晶...

[1975]

[1975] - 关于步进驱动芯片的选型

[920]

[920]

官方公众号

智造工程师

-

客服

客服

-

小程序

小程序

-

公众号

公众号

工控网智造工程师好文精选

工控网智造工程师好文精选