【仙人掌科技工业级闪存卡-小知识】SLC对比MLC与技术发展的影响~! 点击:318 | 回复:0

1. 简介

闪存技术发展至今,传统的存储技术是每个存储单元存储一位二进制数据,如SRAM, DRAM, EEPROM等,这种闪存技术被称作SLC。

在高容量与低成本的推动下,便设计了新型的闪存单元,每个单元能存储多位二进制数据,这种闪存技术最主流的就是MLC,每个单元它能存储2位数据,市场上也能见到TLC,每个单元可以存储3位数据,TLC的耐力相当差,大约300次循环。因此TLC不适合工业应用是一个公认的事实,即使有控制器与软件帮助增加耐力与循环次数。

因此在本白皮书,我们致力于SLC与MLC的关键不同点,及这2款闪存的技术节点制程缩小的含义。

2. 每位(bit)占用的空间与价格

MLC闪存每个单元存储2位数据,较高的存储密度意味着,相同数量的存储器,MLC的存储阵列尺寸比SLC小,较小的存储阵列尺寸只需要小的晶圆,因此每位的成本较低。

尽管MLC有这方面的优势,其容量也不到SLC的2倍,因为MLC需要有复杂的编程与读取电路,晶圆的一些区域就被这些电路消耗掉。

3.设备性能

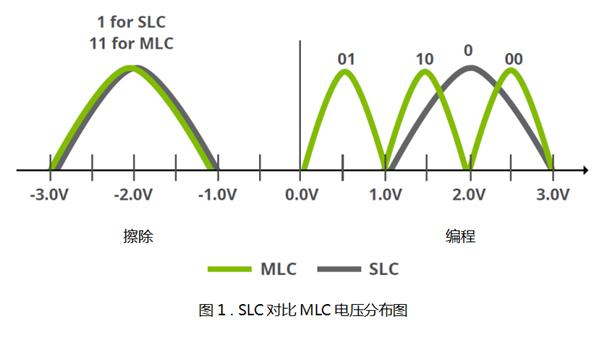

MLC的存储单元为了存储2位数据,在设备的浮栅编程电路必须能够放置4种精确的电荷量,与SLC相同的阀值电压却利用的相当多。图1显示了SLC对比MLC的Vt分布结果。

为了实现在浮栅精确分布电荷,闪存设备需要一个更复杂与更多时间的编程算法这样就会导致MLC编程时间比SLC慢4倍。

读操作也存在类似的性能缺点,因为读取感应电路需要花较长的时间来准确的区分这4种状态,因此,MLC的读处理时间比SLC慢3倍。

4. 系统性能

除了以上描述的根本性能缺陷,MLC闪存还需承受低端的系统的性能,主要是系统对MLC的2个支持缺陷:复制编程与局部编程。

复制编程允许用户移动一页的数据从闪存内部的一个地方到另外一个地方,但没有数据的传入或传出闪存。对一个每页2K字节的闪存来说,每页节省的时间超过170us,复制编程对磨损均衡与读/修改/写操作是最有效的。

局部编程允许用户对页的一部分进行编程,对一个每页2K字节的闪存,应用于电脑来说,一个数据页包含4个数据扇形。在同一时间,局部编程只允许用户编程一个数据扇形,这对读/修改/写操作或者小块数据移动来说,将得到充分应用。

由于MLC的特殊结构与设备特征,其阵列干扰现象更敏感,当访问阵列的一部分时,会导致干扰到同一阵列的其他部分。因此,为了减少陈列干扰,MLC制造商已经禁止局部编程与复制编程,这2个缺陷意味着,当用户需要用MLC将数据从本地的一个地方移动到本地的另外一个地方将非常缓慢,也意味着在进行小块操作时MLC比SLC的性能差很多。

5. 耐力

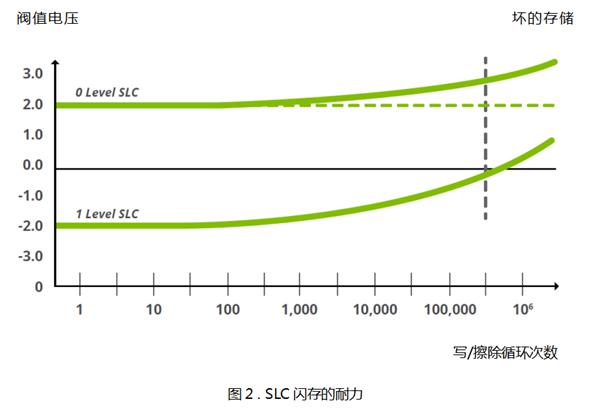

闪存存储单元编程的过程,其实是薄氧化层物理损伤的过程,将导致浮栅从基底慢慢分离。当编程/擦除循环次数不断增加,从而这个损伤不断累加,导致区分编程状态与擦除状态的电压变小,当擦除电压上升到读取检测电压,将会导致读取错误。SLC的这个现象如下图2。

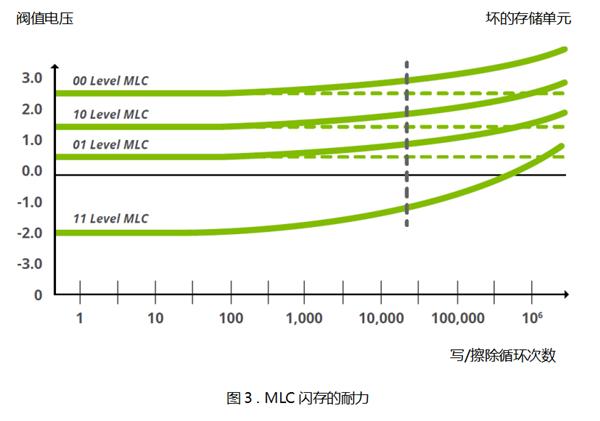

对比SLC,在相同的电压值MLC需要区分4种不同的状态,可利用的窗口的尺寸只有约SLC的一半,由于MLC的编程机制与SLC一样,编程期间对氧化层的损伤程度也一样,又由于编程/擦除窗口只有SLC的一半,意味着MLC比SLC有效编程/擦除窗口变窄的非常早,

如图3:

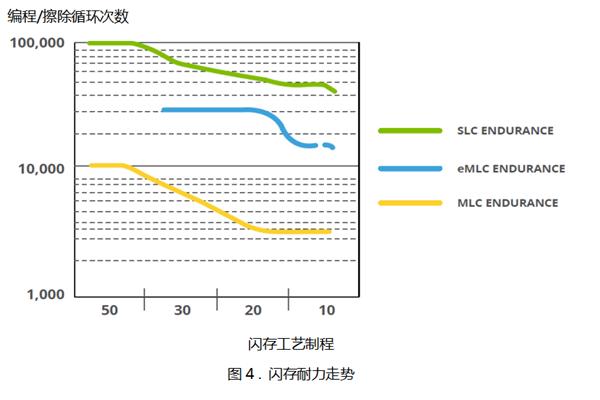

目前SLC工艺一般在30-40纳米,每个存储单元最小的编程/擦除循环次数大约70000次,相比之下,MLC工艺一般在14-20纳米,每个存储单元仅3000次编程/擦除循环,这比SLC低一个数量级,这个差异会随着闪存工艺制程的持续缩小而变的更差,图4显示了耐力与工艺制程之间的关系。

MLC的低耐力意味着不适合频繁数据更新的应用,及苛刻工作条件下的高可靠性要求。

6 企业级MLC

为了解决MLC的低耐力问题,一些制造商提供了企业级MLC或简称eMLC的产品,这类闪存与标准MLC的制造工艺相同,但有不同的编程/擦除算法,对比标准MLC,eMLC有较高的耐力,为了确保在编程状态有足够的电压裕量,因此需要更精确的程序算法,从而导致性能较低。

值得注意的是,图4显示了在相同的工艺制程,eMLC的耐力少于SLC的一半,对于那些长耐力与长产品生命周期的应用来说,SLC一直是一个很好的选择。

7 误码率

上一节已经说明,MLC的电压阀值窗口比SLC小很多,因此MLC对读取感应错误与干扰错误更敏感,由于重复的编程/擦除或者温度变化,阀值电压会上升超过检测阀值而导致感应错误。发生干扰错误是由于记忆体阵列里面,相邻的存储单元交错耦合的影响。产生这2个干扰错误的主要源头,我们将在下文讨论。

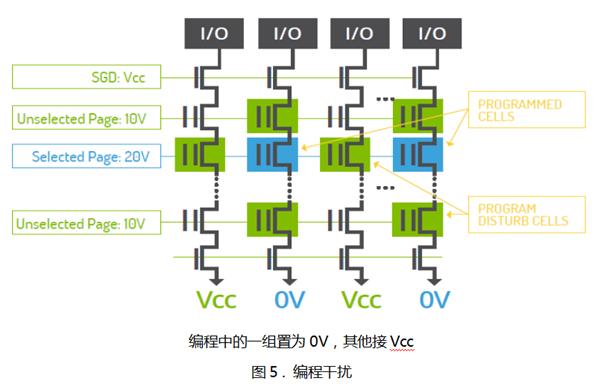

7.1 编程干扰

一个存储单元被编程,附近的存储单元都会发生编程干扰。这是因为附近的存储单元暴露在较高的电平下,因此这些存储单元很容易被编程,图5说明了这个问题:

由于MLC每个状态(4个状态)之间较小的电压裕量,MLC对编程干扰问题更敏感。

7.2读取干扰

一个存储单元被读取,由于杂散电荷被耦合到未选择到的存储单元的浮栅,附近的存储单元就会被读取干扰。这个问题不会跟写干扰一样严重,但是由于闪存制程缩小也会出错。

如图6分析:

根据耐力的实际情况,由于闪存工艺制程的缩小,读与写产生的干扰都会导致错误,

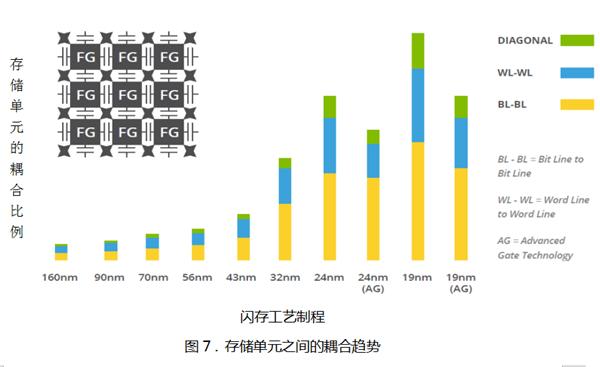

图7显示了存储单元之间的耦合影响vs工艺制程之间的关系:

因为这些问题,近来,仙人掌科技在工业级产品上均使用30-40纳米制程的SLC闪存,而不是14至20多纳米的主流MLC闪存,根据上图,14至20多纳米存储单元间的耦合影响是30-40纳米闪存的3-5倍。

在工业级应用中更需要注意存储单元之间的耦合影响,及外部电压与环境温度导致存储单元漏电与电压裕量改变而情况恶化。

8 总结

在上面章节,我们探索了SLC与MLC的一些关键不同点,当闪存工艺制程缩小时会影响哪些关键可靠性的参数。重点只需记得MLC在高容量低成本方面有一些优势,但是它的性能、耐力,可靠性都很低,仙人掌科技确信SLC在工业级环境应用中能提供优越的性能、耐力与可靠性,因此,仙人掌科技在工业级闪存存储产品中只使用SLC。

控制器制造商已经意识到这些缺陷,提出了很多方法与算法来补偿,得益于先进的算法,MLC的耐力比未使用算法的闪存提高了10倍以上,这个改善或许可以满足一部分应用,即使如此,需要重点注意的是,如图4,即使14-20纳米的MLC的耐力提高了10倍,也少于30-40纳米的SLC的一半。

仙人掌科技确信只有SLC能在工业环境操作中提供优越的性能、耐力与长期的可靠性,因此,仙人掌科技在工业级闪存存储产品中只使用SLC。

我们希望本白皮书能帮助我们的客户能更好的理解SLC与MLC的关键不同点,任何我们的读者有更深入的问题,随时欢迎联系我们的销售部门.

中国:sales@cactus-tech.cn

亚太:info@cactus-tech.com

美国:americas@cactus-tech.com

欧洲/中东/非洲:info@cactus-tech.com

文章原创:工业级闪存专家仙人掌科技

楼主最近还看过

- 求助:增加系统总线上的驱动能...

[3323]

[3323] - Phar Lap ETS™ – 工业...

[1448]

[1448] - 基于51单片机的温度测量系统

[1177]

[1177] - 想学单片机开发,愿和大家探讨...

[4834]

[4834] - 想做电子设计项目兼职或者有...

[4857]

[4857] - 高效、低成本的32位嵌入式网络...

[1945]

[1945] - S3C6410裸机开发教程--RVDS环...

[2511]

[2511] - 遗传算法---(普及知识为人民...

[1404]

[1404] - 测试仪器中怎么用嵌入式PC啊...

[1134]

[1134] - Unix是否可以作为嵌入式系统

[1261]

[1261]

官方公众号

智造工程师

-

客服

客服

-

小程序

小程序

-

公众号

公众号

工控网智造工程师好文精选

工控网智造工程师好文精选