SRAM的基础模块存有三种情况 点击:189 | 回复:0

发表于:2020-09-02 11:43:18

楼主

SRAM是随机存取存储器的一种。“静态”是指这种存储器只要保持通电,里面储存的数据就可以恒常保持。SRAM不需要刷新电路即能保存它内部存储的数据。SRAM功耗取决于它的访问频率。如果用高频率访问SRAM,其功耗比DRAM大得多。有的SRAM在全带宽时功耗达到几个瓦特量级。另一方面,SRAM如果用于温和的时钟频率的微处理器,其功耗将非常小,在空闲状态时功耗可以忽略不计—几个微瓦特级别。本篇内容要介绍的是关于SRAM的基础模块存有三种情况:standby(空余),read(读)和write(写)。

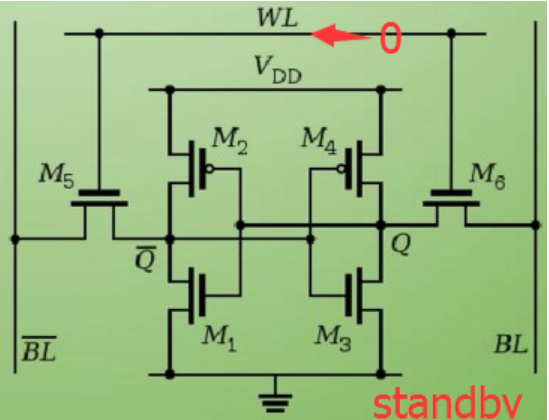

第一种情况:standby

假如WL沒有选为上拉电阻,那么M5和M62个做为操纵用的晶体三极管处在短路情况,也就是基础模块与基准线BL防护。而M1-M4构成的2个反相器持续保持其情况。

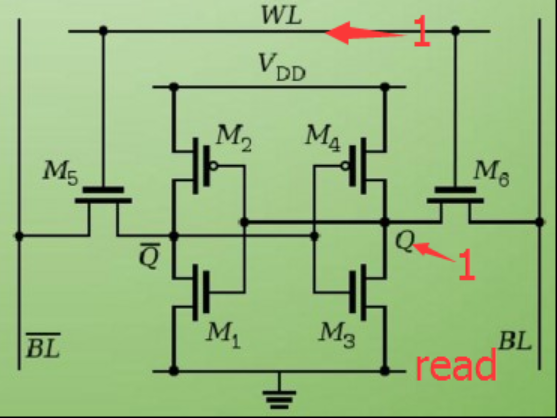

第二种情况:read

最先,假定储存的內容为1,也就是Q处为上拉电阻。读周期时间原始,二根基准线BL,BL#预在线充值为上拉电阻,由于读写能力情况时,WL也会为上拉电阻,促使让做为自动开关的2个晶体三极管M5,M6通断。

随后,让Q的值传送给基准线BL只到预充的电位差,另外泄排掉BL#预充的电。从总体上,运用M1和M5的通道立即连到低电频使其数值低电频,即BL#为低;另一方面,在BL一侧,M4和M6通断,把BL立即拉升。

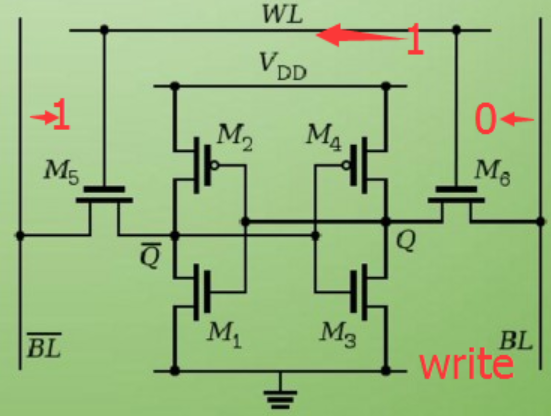

第三种情况:write

写周期时间刚开始,最先把要载入的情况载入及时线BL,假定要载入0,那么就设定BL为0且BL#为1。随后,WL设定为上拉电阻,这般,基准线的情况就被加载sram芯片的基础模块了。深入分析全过程,能够自身画一下。

1分不嫌少!

赏

楼主最近还看过

热门招聘

相关主题

- 哪位能告诉一下6pin的usb接口...

[1832]

[1832] - 初学者如何学习嵌入式系统

[1052]

[1052] - 如何安装组态王嵌入版

[1303]

[1303] - MCGS嵌入式组态软件面市--华...

[1248]

[1248] - 7188问题,编译过程,高手赐教...

[1063]

[1063] - 寻找采集卡

[977]

[977] - 请教一个非常低级的问题

[1062]

[1062] - 中小控制系统数据库选择

[1124]

[1124] - 聊聊VXWORKS好伐?

[1046]

[1046] - stc单片机

[1102]

[1102]

官方公众号

智造工程师

-

客服

客服

-

小程序

小程序

-

公众号

公众号

工控网智造工程师好文精选

工控网智造工程师好文精选