BiSS协议优点和主机实现方法 点击:8942 | 回复:4

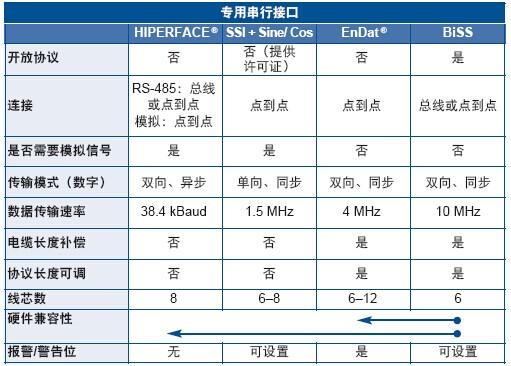

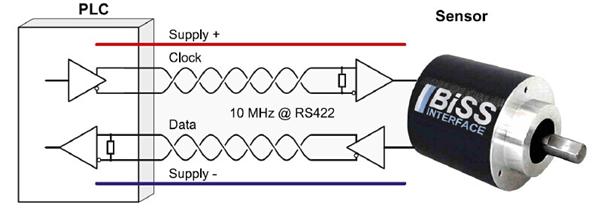

BiSS(双向同步串行接口)是一种开放协议,也是最新的编码器接口。它的原理有所不同:无论控制器请求与否,BiSS都会发送完整的绝对位置信息,而不光是在系统启动阶段。这使系统在运行时能够很容易地从短暂数据丢失故障中恢复回来。由于是全数字系统,它能够省却了驱动系统使用某些传属协议连接编码器所需的A/D转换器成本。BiSS与SSI是硬件兼容的,互换时只要更改软件即可。BiSS有4根数据线(1对编码器时钟输出线,另1对是编码器数据输入线),另外还具有2根电源线。BiSS允许上位机访问编码器内部寄存器来读写与编码器相关的数据(标识、设备数据、分辨率等)。它还能在不影响实时运行的情况下,根据需要将其它数据(温度、加速度等)传送至上位机。BiSS与HIPERFACE一样,能够通过点对点或总线进行接。

为什么实施BiSS?

一个完整的BiSS系统结构

图1:BiSS系统(点对点配置:主机,电缆,从机)

使用BiSS的好处

开放的标准

非专有

快速

串行

安全

点对点能力

多从机总线能力

紧凑

高性价比

双向

采用单向线(例如RS422)

SSI 物理兼容

SSI向后兼容/向下配置的主机和从机

准备好能使用的IP模块给设备制造商

设备制造商免费使用许可证

使用现有的 EnDAT 2.2™硬件

EnDAT 2.2™使用RS485。典型的EnDAT 2.2™PHY硬件允许双向操作在每一条线。BiSS只需要单向操作每一条线作为EnDAT 2.2™PHY硬件的一个子集。BiSS接口可以使用现有的EnDAT 2.2™PHY硬件实现。

使用现有的SSI硬件

SSI使用RS422单向线驱动。典型的SSI PHY硬件允许单向操作每一条线。BiSS也只需要单向操作每一条线,与SSI PHY硬件兼容。BiSS接口可以使用现有的SSI PHY物理硬件实现。

使用现有的FPGA硬件

BiSS主机IPs MB101和MB105是可用的,VHDL基于BiSS主机实现,以CPLD/FPGA硬件为基础。

FPGA平台实现BiSS 主机IPs

ALTERA

XILINX

ACTEL

Lattice

其它和新的平台,支持VHDL或NET LISTS

使用现有的DSP /μC / CPU硬件

BiSS主机IPs MB302是C / C + +代码基于BiSS主机实现在DSP /μC / CPU硬件。

DSP /μC / CPU平台,实现了BiSS主IPs

Microchip PIC™

Texas Instruments

SiLabs

其它和新的平台,支持C / C + +代码/结构化编程代码

DSP / μC / CPU输出/输入接口

GPIO:2引脚(MA GPIOx输出,SL GPIOy输入)

SPI:2引脚(MA = SCLK,SL = MISO)

其他串行协议发生器硬件

使用现有的IC硬件

iC-MB3 TSSOP24

iC-MB4 TSSOP24

定制ASICs

采用BiSS主机功能的未来产品

- 伺服控制技术中的死区及死区...

[5420]

[5420] - 刘工,能不能谈一下方波伺服和...

[8960]

[8960] - 求教:光电开关和接近开关的区...

[8116]

[8116] - 求解:如何多次使用三菱PLC中...

[7741]

[7741] - RMS是什么意思

[7332]

[7332] - 如何用PLC+2台变频器+2个编码...

[8526]

[8526] - 伺服电机为什么不能直接接交...

[6525]

[6525] - 手摇脉冲发生器A和B的电压问...

[8412]

[8412] - 什么是PDFF控制?

[6559]

[6559] - 多圈编码器与单圈编码器的区...

[21176]

[21176]

官方公众号

智造工程师

-

客服

客服

-

小程序

小程序

-

公众号

公众号

工控网智造工程师好文精选

工控网智造工程师好文精选